本文為明德揚原創文章,轉載請注明出處!

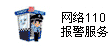

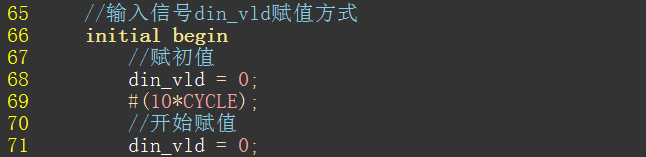

MDY有一條非常重要的看波形技巧,即“時鐘上升沿前看條件”的技巧,意思就是在時鐘上升沿前,看條件信號,看到什么值就是值。

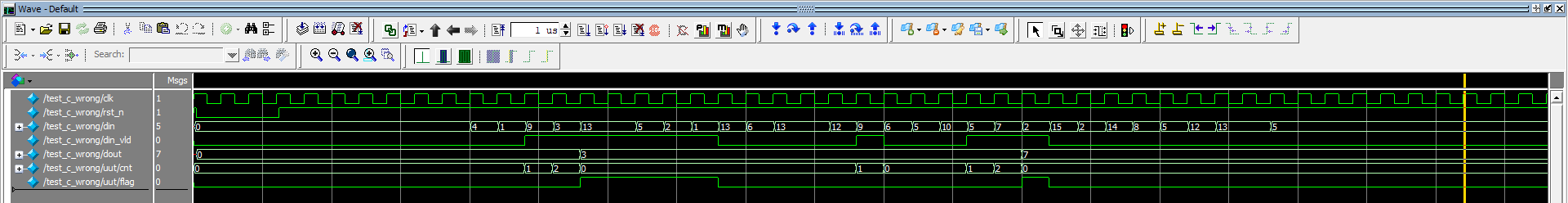

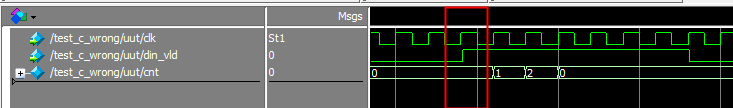

如下圖所示:

這一條技巧,對于剛學習FPGA的人來說,非常之實用。

但是,部分工程師在做仿真時,有時候會出現違反這一原則的奇怪現象。例如下面這個案例。

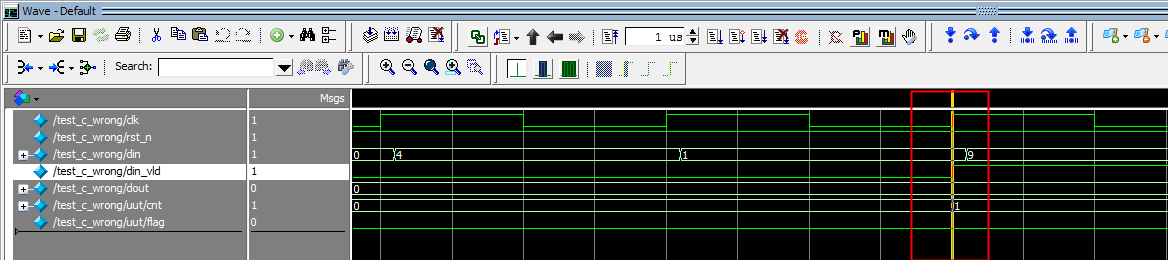

關于在仿真軟件中,為什么計數器的判定會在不滿足加一條件的時候進行加一操作(如下圖所示)。計數器cnt_col的加1條件是din_vld,按照原則,第4個時鐘上升沿的時候,din_vld應該為0,計數器不應該加1,但事實上是加1了,這是怎么回事?我們舉另一個例子來說明這個問題。

功能要求如下:復位后,din_vld 不定時等于1,當din_vld出現3個或超過3個周期的高電平脈沖時,將第三個周期時對應的din值賦給dout,其他時候dout保持不變。

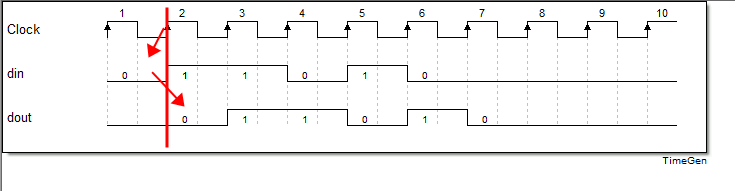

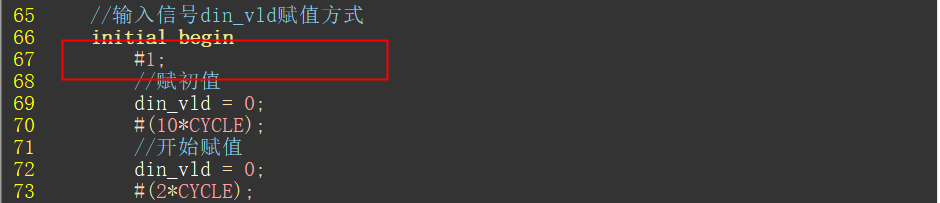

根據功能要求,寫出代碼后用modelsim進行仿真,效果如下圖:

然后發現仿真的波形和我們預期的波形并不一致!!

計數器cnt在din_vld == 0 的時候就已經開始計數了。

查看代碼,計數器cnt的加一條件是:add_cnt = din_vld == 1 && flag == 0 。

也就是說,信號din_vld在時鐘上升沿處由0變1的時候,仿真軟件把信號din_vld的值取為1了。

那么會出現這種情況的原因是什么呢?

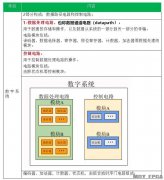

這里是軟件仿真,是軟件模擬真實的電路情況。但是,軟件模擬是有缺陷的,無論軟件如何模擬,本質上它都是串行執行的代碼,是一條一條指令執行的。

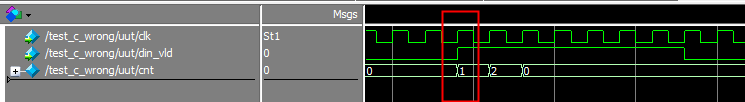

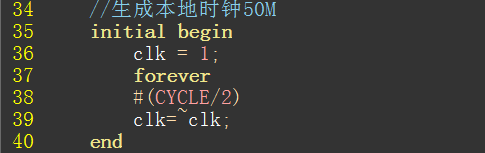

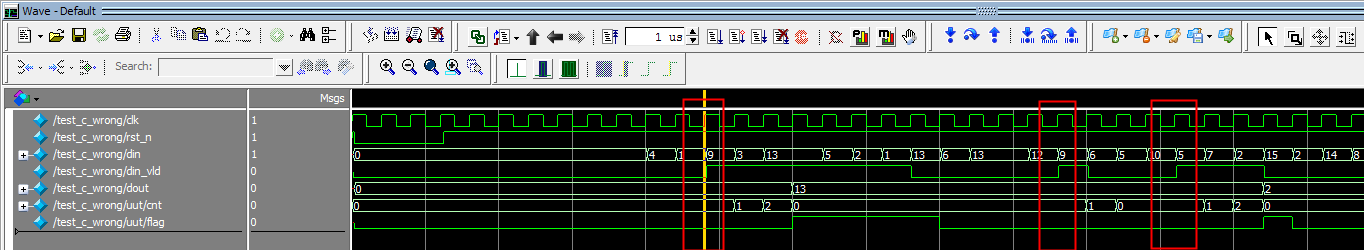

在仿真文件里,有兩個initial語句,一個是產生時鐘的,一個是產生din_vld的,如下圖。

按照verilog的語法,這兩個initial是并行執行的。但事實上軟件執行是有先后的。很有可能先執行了din_vld變1的代碼,再執行了clk由0變1的代碼,這種情況下,在時鐘的上升沿就會采到din_vld為1,因此就會出現案例中的錯誤。

這是與FPGA實際的電路是不符合的,也就是說這個其實是仿真缺陷的問題,而不是設計問題。

雖然不是設計問題,但仿真仍然要繼續,我們需要避免這種情況。如何避免呢?

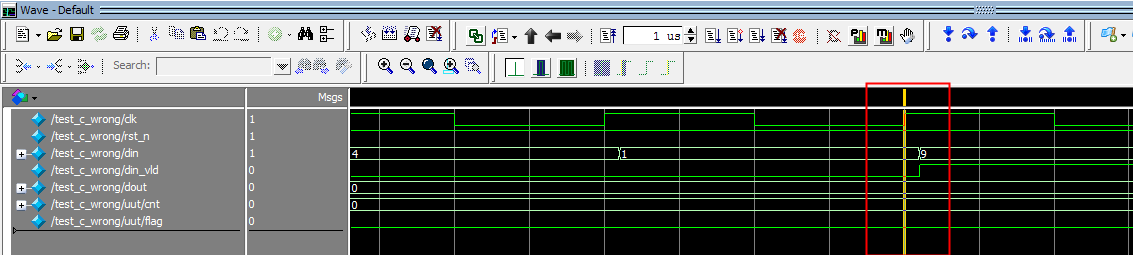

解決上述問題的方法:我們可以在測試文件中給信號加上一個1ns 的延時,這樣兩個initial語句就絕對不會同時執行。

代碼如下圖:

用modelsim重新編譯一下再仿真,此時的波形就是功能要求的正確結果。如下圖:

Bingo!!!問題完美解決。