Lattice MIPI D-phy 硬件設(shè)計

本文為明德?lián)P原創(chuàng)文章,轉(zhuǎn)載請注明出處!作者:鄭先生

MIPI聯(lián)盟是一家合作的全球性組織,為開發(fā)移動和受移動設(shè)備影響的行業(yè)提供服務(wù)。該組織的重點是設(shè)計和推廣硬件和軟件接口,以簡化從天線和調(diào)制解調(diào)器到外圍設(shè)備和應(yīng)用處理器的設(shè)備內(nèi)置組件的集成。MIPI Alliance精心設(shè)計其所有規(guī)格,以滿足移動設(shè)備所需的嚴格操作條件:高帶寬性能,低功耗和低電磁干擾(EMI)。 所有領(lǐng)先的芯片組供應(yīng)商都使用了MIPI Alliance規(guī)范,這些規(guī)范已幫助移動行業(yè)的公司整合了集成方法,同時創(chuàng)建了自己的高級設(shè)計來使產(chǎn)品與眾不同。當(dāng)今市場上的每個智能手機都至少具有一個MIPI Alliance規(guī)范。

Lattice Xilinx 等FPGA芯片原廠都是其聯(lián)盟成員,MIPI聯(lián)盟發(fā)布了很多接口規(guī)范標準,其中MIPI CSI-2,MIPI DSI,是目前廣泛應(yīng)用的接口標準,主要應(yīng)用在移動端,例如移動電話,平板電腦等,近些年也廣泛應(yīng)該于汽車領(lǐng)域,工業(yè)領(lǐng)域,主要還是ADAS ,機器學(xué)習(xí)的興起。

MIPI CSI-2 (MIPI Camera Serial Interface 2),移動和其他市場中使用最廣泛的攝像機接口。它以其易用性和支持廣泛的高性能應(yīng)用程序(包括1080p,4K,8K以及更高的視頻和高分辨率攝影)而得到廣泛采用。其由協(xié)議層,應(yīng)用層,物理層構(gòu)成。物理層使用的是D-phy (主要還是D-phy)跟C-phy。

MIPI DSI(MIPI Display Serial Interface)定義了主機處理器和顯示模塊之間的高速串行接口。該接口使制造商能夠集成顯示器以實現(xiàn)高性能,低功耗和低電磁干擾(EMI),同時減少引腳數(shù)并保持不同供應(yīng)商之間的兼容性。設(shè)計人員可以使用MIPI DSI為最苛刻的圖像和視頻場景提供出色的色彩渲染,并支持立體內(nèi)容的傳輸。其物理層也是采用的D-phy

D-phy 是MIPI聯(lián)盟的物理層小組所發(fā)布的物理層標準,該小組還發(fā)布其他物理層標準, A-phy , C-phy , M-phy。

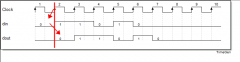

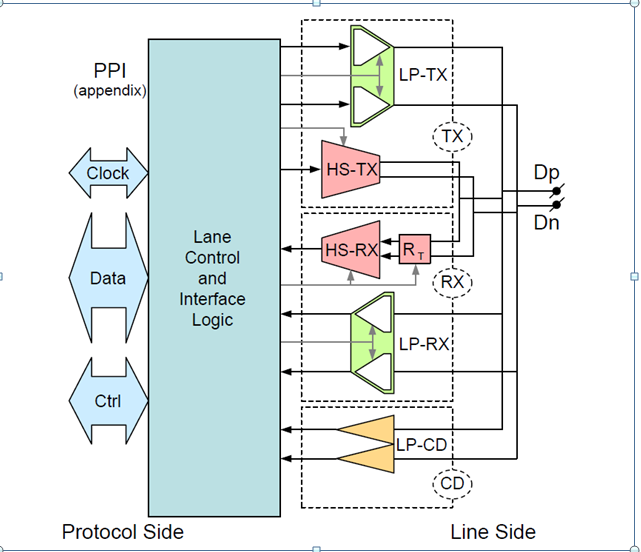

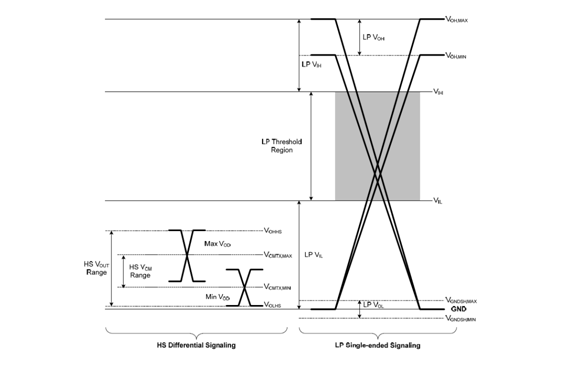

D-phy V1.0 標準指出,其使用了兩種傳輸數(shù)據(jù)的模式,高速模式(High Speed,HS)和低功耗模式(Low Power,LP),兩種模式使用不同的傳輸電平和傳輸機制。D-phy每個數(shù)據(jù)通道使用兩條線(HS跟LP在每個通道下是共用的傳輸線),時鐘通道使用兩條線。這說明了用于最低配置的時候需要四根線。 在高速模式下,每個通道在兩側(cè)均終止,并由低擺幅差分信號(SLVS)驅(qū)動。 在低功耗模式下,所有電線均采用單端和非終端方式操作。

在HS模式下其速率可達到500Mbps,DDR(dual-edged data transmission)模式。通過采用突發(fā)模式通信,可以降低有效數(shù)據(jù)吞吐量。 低功耗模式下的最大數(shù)據(jù)速率為10Mbps。

D-PHY電氣子層指出高速信號(HS)采用的差分電平傳輸?shù)臄[幅較低,一般為200 mV,而低功耗信號(LP)單端電平傳輸?shù)臄[幅較大,一般為1.2V。

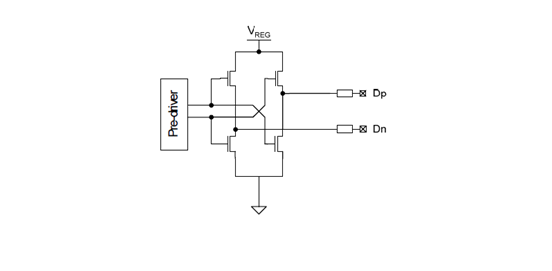

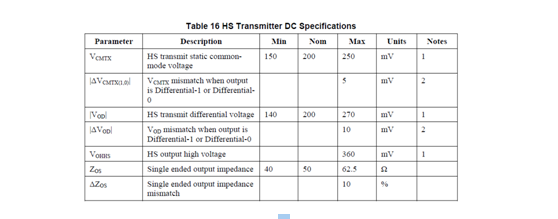

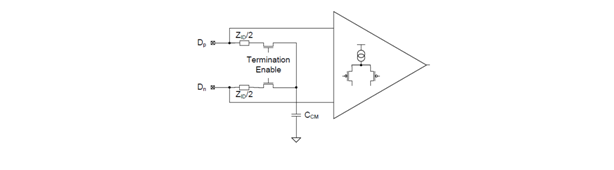

HS的發(fā)送端的電路結(jié)構(gòu)如圖,是由兩個CMOS組成的差分輸出電路,由其DC參數(shù)可以得到,其差分壓擺幅度是140~270mV,一般值為200mV,單端輸出阻抗為40~62.5 ohm,這個參數(shù)可以幫助我們設(shè)計接收端電路板時做好阻抗控制與匹配,以保證信號完整型。Lattice FPGA內(nèi)部并沒有這樣的IO buffer,所以只能通過使用其他的IO buffer 做電平轉(zhuǎn)換,以滿足這樣的要求。

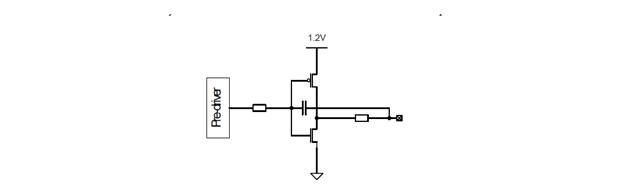

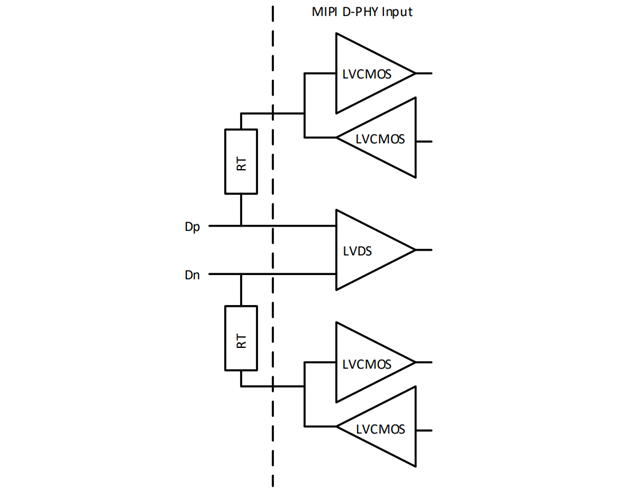

LP的發(fā)送端電路圖,其為LVCOMS12結(jié)構(gòu)輸出,Lattice FPGA 擁有LVCOMS12 IO buffer,加上外部端接電阻,可以滿足輸出阻抗110 Ohm的要求。

HS與LP的接收端與普通的LVDS,CMOS接收端并無多大區(qū)別。由于Lattice 可以接收200mV的SLVS,只要選擇固定的IO bank就行,值得一提的是Lattice 器件的tureLVDS 管腳有限,使用LVDS25E需要外接端接電阻,端接電阻Zid一般為100 ohm,與LVDS外部端接保持一致。當(dāng)然,LVDS 跟LVDS25E所能接收的速率是不一樣的,這一點需要注意。

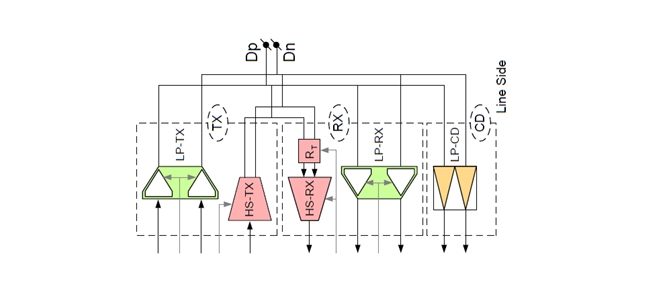

Lattice MIPI csi-2與 DSI 除了使用crosslink器件解決方案,其他器件都需要自己添加與設(shè)計D-phy的電氣子層,因為crosslink器件更像一個可編程的ASIC,普通的FPGA是沒有下圖這樣的物理資源。

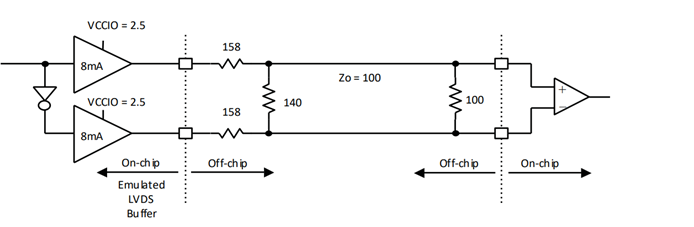

MIPI D-phy 發(fā)送端的設(shè)計需要使用到LVDS25E的資源,LVDS25E是通過 Lattice 的8mA CMOS輸出buffer,構(gòu)成的橋式電路。通過外部電阻構(gòu)成的分流網(wǎng)絡(luò),可以模擬出LVDS 的輸出。

改變這個電阻網(wǎng)絡(luò),可以模擬出D-phy HS 輸出電平與LP電平,LP電平使用的 IO buffer 為LVCMOS12。Lattice官方給好的數(shù)據(jù)是RH=330 ohm ,RL =50 ohm,當(dāng)然該bank的電源要使用2.5V,若使用3.3V,則需要根據(jù)速率與信號完整性自己進行設(shè)計。

對于接收端,由于Lattice 的LVDS IO buffer 支持SLVS 電平,只需要在LP接收端使用LVCMOS12 的 IO buffer,且外部添加RT=50 ohm的端接電阻即可。當(dāng)LVDS IO資源不夠時,可以采用LVDS25E,這將需要外端接100 ohm電阻,并且MIPI CSI-2跟MIPI DSI 的工程綜合后,布局布線會報錯,這時則需要自己優(yōu)化好FPGA內(nèi)部布局布線等。

目前明德?lián)P公司已經(jīng)使用Lattice MachXO3系列與ECP5系列完成了4路sensor 通過MIPI csi-2 輸入,拼接成一路MIPI CSI-2輸出的工程,該工程也應(yīng)用于無人機,工業(yè)機器視覺等開發(fā)。想要合作的朋友可以聯(lián)系明德?lián)P!