本文為明德?lián)P原創(chuàng)文章,轉(zhuǎn)載請注明出處!

一、摘要

明德?lián)P(MDY)在某個XILINX項(xiàng)目中,偶然性出現(xiàn)開機(jī)后通信出錯的情形,具體表現(xiàn)為反復(fù)開機(jī)測試400次后,約有1~2次通信異常,數(shù)據(jù)發(fā)不出去。經(jīng)過定位,是某個FIFO出現(xiàn)異常,時鐘正常、復(fù)位無效、寫使能有效的情況,空信號empty一直為1,即一直保持為空的問題。

二、項(xiàng)目背景

FIFO是FPGA項(xiàng)目中使用最多的IP核,一個項(xiàng)目使用幾個,甚至是幾十個FIFO都是很正常的。通常情況下,每個FIFO的參數(shù),特別是位寬和深度,是不同的。如果按照通常做法,每種位寬和參數(shù),都要打開FIFO IP核界面、命名(命名不好不好分辨需要的FIFO)、設(shè)置參數(shù)、生成并編譯IP核,工作量可以想象出來是非常多的。

明德?lián)P(MDY)在2021年承擔(dān)了多個基于XILINX芯片的研發(fā)項(xiàng)目,包括VPX網(wǎng)絡(luò)透明傳輸項(xiàng)目(芯片為XC7K325T-2FBG900)、某高端測試儀項(xiàng)目(芯片為XCKU060-FFVA1156)、某網(wǎng)閘設(shè)備項(xiàng)目(芯片為XC7Z030-FBG676)等,另外,明德?lián)P自研了基于XC7K325T-2FBG900和基于XC7K410T-2FBG900芯片的核心板,在XILINX研發(fā)領(lǐng)域擁有豐富的經(jīng)驗(yàn)。

對于我們專門承接項(xiàng)目的團(tuán)隊(duì),絕不可忍受如此重復(fù)、枯燥、容易出錯的工作。經(jīng)過精心研究,終于發(fā)現(xiàn)XILINX的原語:xpm_fifo_async,是可以可參數(shù)化FIFO的位寬和深度的。即在設(shè)計時,不用生成FIFO IP,直接例化xpm_fifo_async,例化時定義好位寬和深度,就可以使用了。關(guān)于具體的使用方法,可以留意我們新出的文章教程。

本問題的出現(xiàn),就是在使用這個xpm_fifo_async時出現(xiàn)的。

三、問題現(xiàn)象

FPGA問題都不好定位,特別是偶然性出錯的問題,即使復(fù)現(xiàn)問題都要花大量精力。本問題出現(xiàn)的概率小于1%,即使概率如此之低,也是不得不去定位去做的工作。

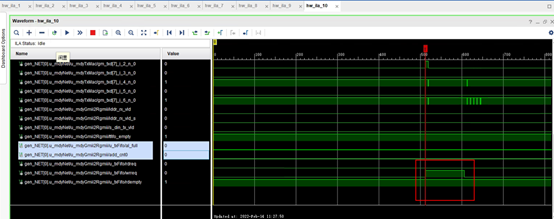

在花費(fèi)了一個月的時間,才定位到某個FIFO出現(xiàn)異常。為更加細(xì)致地確認(rèn)是FIFO哪里出錯,使用ILA抓取FIFO的信號,包括寫使能、復(fù)位、空指示信號等。

如上圖所示,在FIFO寫使能有效時,empty信號仍然保持為空狀態(tài),導(dǎo)致數(shù)據(jù)無法傳輸。更奇怪的是,即使復(fù)位了這個FIFO,仍然是同樣現(xiàn)象。

四、問題分析

該問題非常之奇怪,從邏輯角度講,時序是正確的,那么IP核就應(yīng)該正確,是不應(yīng)該出現(xiàn)此問題的。

懷疑是FIFO使用不正確,如FIFO滿后還在寫,或者FIFO空后仍在讀。特意在ILA觸發(fā)寫使能、寫滿信號同時為1,看兩者是否有同時有效,沒有觸發(fā)到,說明沒有問題。

懷疑是寫時序不正確:為此,我們還反反復(fù)復(fù)地觀測寫時序,捕捉開機(jī)后的第一個寫時序,也是沒問題的。

懷疑處于復(fù)位狀態(tài):為此觀測復(fù)位信號,發(fā)現(xiàn)沒有處于復(fù)位狀態(tài),沒有問題。

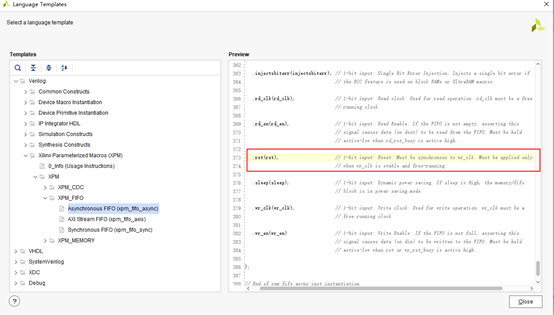

在思考了多種辦法后,問題沒有解決。為此,不得不認(rèn)真查閱xpm_fifo_async的官方資料,查看步驟:

vivodo-PROJECT MANAGER-Language Templates-Verilog-Xilinx Parameterized Macros(XPM)-XPM-XPM_FIFO-Asynchronous FIFO (xpm_ fifo async)。

通過調(diào)閱vivado中有關(guān)FIFO的說明,終于發(fā)現(xiàn)了問題。

如上圖所示,復(fù)位信號rst要求同步于WR_CLK時鐘。而我們的復(fù)位信號是異步信號,不滿足要求。

五、解決方法

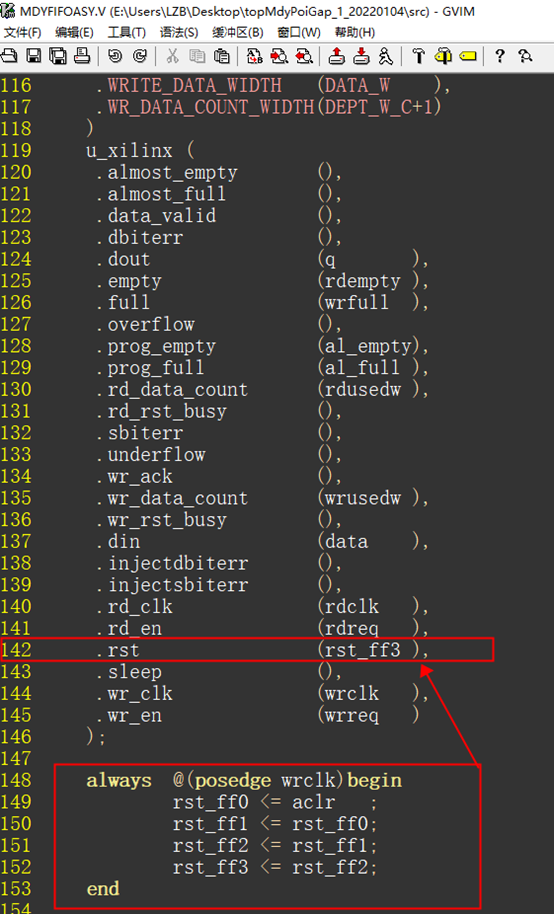

對 FIFO中的復(fù)位信號進(jìn)行異步信號同步化處理,即對復(fù)位信號進(jìn)行延遲兩拍處理,如下圖所示:

上圖中,aclr是異步復(fù)位信號,經(jīng)過上圖中的148~153行的代碼,將該信號同步化,同步化后的rst_ff3可以認(rèn)為同步于寫時鐘。將該信號連接到rst中,如圖中的第142行。

每3分鐘重啟一次,經(jīng)過三天的嚴(yán)苛測試,再沒有出現(xiàn)通信異常問題,問題得到解決!!!

溫馨提示:明德?lián)P2023推出了全新課程——邏輯設(shè)計基本功修煉課,降低學(xué)習(xí)FPGA門檻的同時,增加了學(xué)習(xí)的趣味性,并組織了考試贏積分活動

http://m.cqqtmy.cn/ffkc/415.html

(點(diǎn)擊→了解課程詳情?)感興趣請聯(lián)系易老師:13112063618(微信同步)

明德?lián)P除了培訓(xùn)學(xué)習(xí)還有項(xiàng)目承接業(yè)務(wù),擅長的項(xiàng)目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(IMX472 IMX492)

3. PCIE采集系統(tǒng)

4. 圖像項(xiàng)目

5. 高速多通道ADDA系統(tǒng)

6. 基于FPGA板卡研發(fā)

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關(guān)信息可以聯(lián)系:易老師13112063618(微信同號)