本文為明德揚原創文章,轉載請注明出處!

一、項目背景

明德揚(MDY)為中科院某所研制一款X射線采集和處理設備,該設備采用了AD8488和AD9244兩款芯片進行X射線的采集,采用FPGA進行處理,并通過網口上送至上位機處理。

本文介紹了AD8488和AD9244的原理,下一篇文章將介紹X射線采集中遇到的問題,希望能對大家有所幫助。明德揚專注于FPGA方面的項目研發以及相關元器件銷售,有相關需求的,可聯系我們。

二、AD8488簡介

AD8488是一款128通道模擬前端,為高性能數字X射線系統而設計。它的模擬通道由一個積分器和增益可選的單端轉低阻抗差分輸出組成。該模擬通道將X射線或光電二極管檢波器收集的電荷轉換成電壓信號。通道由CMOS晶體管組成,這些晶體管采用典型高輸入阻抗的CMOS門。該設備的積分器采用一系列可選電容值,產生與電荷有關的電壓,可適應廣泛的輸入電荷值。單端輸入轉差分輸出電壓放大器位于積分器之后,在這里偏移和低頻噪聲電壓從輸入電壓中減去。一條128:1通道差分MUX位于緩沖器之后,驅動模擬輸出緩沖。同時還提供開關驅動器和某些數字計時功能;這些功能全部集成在255引腳BGA基板上。全部128通道的電荷轉換是同步進行的,之后便采用7位地址編碼生成順序電壓輸出讀數。一共兩次序列,對全部128通道進行采樣。邏輯控制輸入CS_A和CS_B分別選擇通道地址的下限和上限64模塊。

三、電荷積分放大器

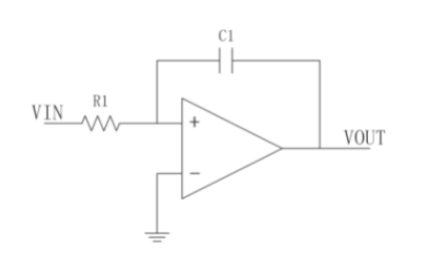

圖1為運放積分放大器的電路圖

圖1:理想積分放大器電路圖

根據運放虛短可知,反向端與同相端電壓相等,又由虛斷可知,通過R1的電流與通過C1的電流相等。通過R1的電流為:

由此可得,運放的輸出電壓等于對輸入電壓在時間上的積分。若輸入端為電荷采集裝置的話,那么運放的輸出與輸入端的電荷量成正比。兩部分組合起來就是電荷積分放大器。

四、AD8488工作原理

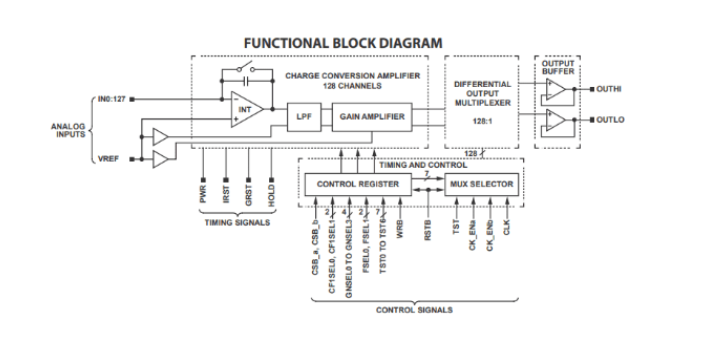

AD8488電路結構如圖2所示:

圖2:AD8488電路結構圖

如圖所示,AD8488主要由四部分構成。分別為前置電荷量轉換器、差分輸出選擇器、輸出緩沖器和時序/控制部分。

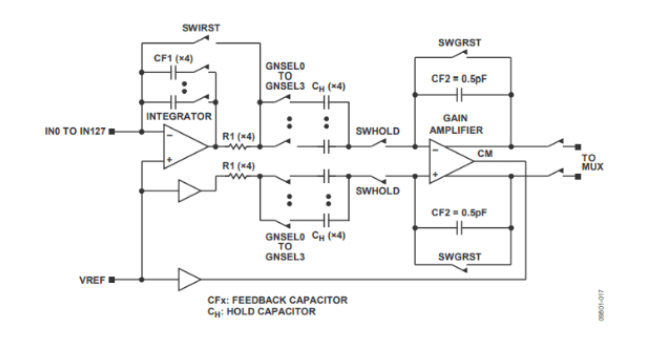

前置電荷量轉換器為128通道電荷積分放大器,每一個通道由一個放大器,一個低通濾波器和一個二級放大器構成。電路結構圖如圖3所示:

圖3:電荷量轉換器結構圖

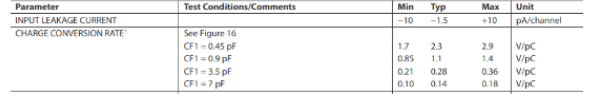

前端采集到的電荷信號通過第一級積分放大器進行轉換,共有四檔可選。各檔位轉換參數如圖4所示:

圖4:電荷積分放大器轉換參數

這四檔分別由四種不同容值的反饋電容(CF1)控制。當CF1=0.45pF時,輸出典型值為2.3V/pC(單位為伏特每皮庫倫,指每積分1皮庫倫,輸出為1V。1pC==10-12c);當CF1=1.1pF時,輸出典型值為1.1V/pC,以此類推。CF1容值越大,增益越低。

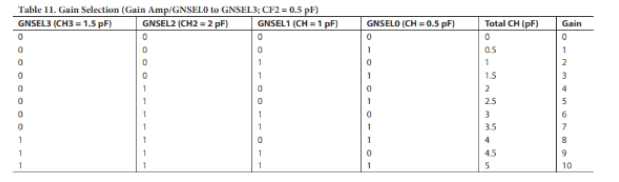

第二級低通濾波器實際上是一個保持裝置,由一個電阻R1和一個電容CH構成。第一級放大器輸出的電壓信號通過R1給電容CH充電,以便于第二級放大器對CH進行積分放大。因此相當于一個低通濾波器。CH的參數由GNSEL[3..0]選擇,參數如圖5所示:

圖5:CH參數選擇表

注:GNSEL[3..0]寄存器只能選擇CH的容值,并不代表增益。上圖中所表示的增益實際上是當二級放大器的反饋電容為0.5pF是,不同的CH容值下對應的增益。

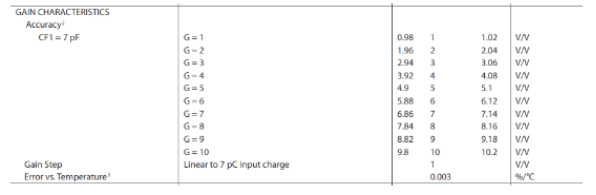

第三級放大器與第一級相同,也是一個電荷積分放大器。只不過第一級輸出的電壓信號是對芯片輸入的電荷量的積分,然后該電壓信號對第二級的CH電容進行充電,之后通過第二級放大器對CH的電荷量積分,最終輸出新的電壓信號,形成二次放大的效 果。第二級積分放大器增益由CF2控制,共有10檔,增益單位為V/V。注:因為第一級放大器已經將電荷信號轉換為電壓信號,因此第二級放大器的電壓為伏特每伏特。增益表如圖6所示:

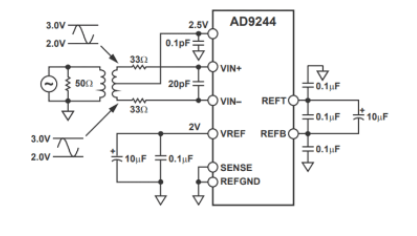

AD8488采集的信號經過兩級放大后,經數據選擇器選通通道后,再由一個緩沖器輸出差分信號。該信號的幅度范圍為1.5V至2.5V。官方推薦使用AD9244這款ADC芯片進行模擬信號轉換,推薦電路如圖7所示:

圖7:AD8488與AD9244連接示意圖

AD8488與AD9244共用一個2.048V的電壓參考。AD9244的差分輸出范圍為0~2.048V,偏置電壓為2.5V。

五、模數轉換部分

模數轉換芯片選用ADI公司的AD9244,是一個14BIT,最高采樣率為65MHz的高速ADC芯片。它由+5V模擬電壓供電,也可以在+3.3V或+5V的數字電壓下正常工作。

AD9244可專門用來處理峰峰值為1~2V的模擬小信號。它的輸入信號和時鐘信號都可以采用差分輸入形式,以使系統獲得最好的性能。14位數字輸出信號可以表示為直接二進制的形式,也可以是二進制補碼的形式。一位溢出表示位(OTR)可以用來輸出 溢出信號,將這一位信號和14位信號中的最高位用一定方式組合起來判定輸入信號是上溢出還是下溢出。

VIN+,VIN-:模擬信號輸入端。采用單輸入形式時,在VIN+端接輸入信號,VIN-端接地;采用差分形式輸入模擬信號時,VIN+,VIN-分別接差分信號的兩端。差分輸入的形式對于高精度高速度的應用更容易獲得好的效果。一般情況下,輸入信號都是 單路形式,因此經常采用1:1變壓器或者專用差分轉換芯片來實現單路信號到差分信號的轉換。

CLK+,CLK-:時鐘信號輸入端。和VIN+、VIN-相似,輸入時鐘也可以采用單輸入和差分兩種輸入形式,不過在AD9244的內部最終都會把單輸入的時鐘信號變為差分形式。輸入時鐘信號的質量對模數轉換的效果有很大的影響,因此應盡量保證時鐘信號 的純凈和準確,并盡量避免對時鐘輸入信號的干擾。

DUTY:時鐘穩定信號。該端接高電平時,可以在內部對外部輸入時鐘的占空比進行調整,以產生占空比準確為50%的時鐘信號。

REFSENSE,VREF,REFGND:內部參考電壓腳。這三個管腳的不同連接可以產生1V~2V的內部參考電壓,在這三個管腳之間連接適當的電阻還可以隨意產生1V與2V之間的任意電壓參考。

REFT、REFB:ADC內部參考電壓去耦管腳。這兩個管腳的輸出電壓是AD9244內部實際的參考電壓值。它們之間應該用10μF的電解電容去耦,同時應并聯一個0.1μF的小電容,這樣效果可能會更好。每個管腳都必須用0.1μF的電容接地。

CML,VR:AD9244內部使用的模擬偏壓點,通常該端會產生大于300μA的電流,因此必須用0.1μF的電容接地以進行去耦。

OEB:輸出允許管腳。AD9244有三態輸出功能。如果OEB接地,那么AD9244的輸出驅動器就會激活,并輸出轉換后的數字信號;而如果OEB接高,輸出信號管腳則輸出高阻態。

DB0~DB13:數據輸出腳,其中DB0為最低位。

OTR:電壓溢出指示管腳。當OTR輸出為1時,表示輸入電壓超過AD所能轉換的電壓范圍。OTR和DB0進行簡單的邏輯組合可以準確地判斷輸入電壓是上溢出還是下溢出。

DFS:輸出數據形式選擇管腳。當DFS接數字地時,輸出數據為直接二進制形式;當DFS接數字電源時,輸出數據為二進制補碼形式。

本設計中的AD9244有以下幾點設計要點:

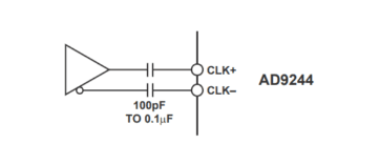

1)時鐘采用差分的方式驅動。由于時鐘信號和ADC的輸出信號在一根排線內,ADC輸出的并行數據會對時鐘產生十分嚴重的影響,因此用差分的方式傳輸時鐘。差分時鐘在控制板上分別由FPGA和AD9517產生,在調試時做二選一,用于驗證兩種時鐘對采樣時序以及信噪比的影響。時鐘與ADC的連接方式如圖8所示:由于控制板產生的時鐘信號為LVDS,因此在AD9244時鐘輸入端做交流耦合即可。

圖8:AD9244差分時鐘輸入(交流耦合)

2)信號輸入方式采用差分模式、直流耦合。AD8848的輸出為差分信號,因此采用差分的形式與AD9244相連,AD9244信號輸入端電路如圖9所示:同時,ADC的VREF采用外部參考電壓2.048V,因此單邊信號輸入的范圍為1Vpp,差分信號的輸入范圍為2Vpp。又因為供電電壓為5V,因此輸入共模電壓為2.5V。

圖9:AD9244信號輸入電路(直流耦合)

3)AD9244模擬供電電壓為5.0V,數字供電電壓為3.3V,這樣就可以省掉電平轉換器,將ADC輸出信號直接與FPGA相連。參考電壓與AD8488共用一個芯片,為2.048V。由于使用了外部參考電壓,所以需要將SENSE腳接高。

AD9244為14位ADC,有效位數約為12BIT,因此在測試時,當差分輸入正負兩端相連,ADC上隨機跳動的比特位應該是2bit,而輸出的數值應該在8192附近跳動。當差分輸入信號峰峰值為2Vpp是,ADC剛好打到滿幅狀態,超過這個電壓,OTR為1, ADC溢出。

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://m.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯系易老師:13112063618(微信同步)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)