在介紹IP核之前,先了解下PCIE是什么?

PCIE是一種高速串行計算機擴展總線標準,屬于高速串行點對點雙通道高帶寬傳輸,所連接的設備分配獨享通道帶寬,不共享總線帶寬,支持主動電源的管理,錯誤報告,端對端的可靠性傳輸,熱插拔以及服務質量等功能。優點有數據傳輸速率高,發展潛力相當大。

一. PCIE IP核

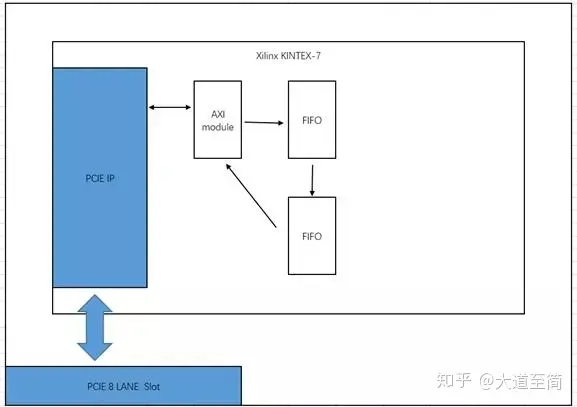

PCI-Express IP核,可以實現PCIE協議物理層到數據鏈路層、再到事務層的協議接口信號轉換。因此這里選擇在PCIE協議 IP核的基礎上,直接在PCIE協議的事務層進行DMA控制器的設計。

IP核是知識產權模塊的意思,EDA開發中具有相當的地位。IP主要分為軟IP、固IP和硬IP。軟IP是用Verilog/VHDL等硬件描述語言描述的功能塊,但是并不涉及用什么具體電路元件實現這些功能。固IP是完成了綜合的功能塊。硬IP提供設計的最終階段產品——掩膜。

IP核將一些在數字電路中比較常用,但是復雜的功能塊,如、SDRAM控制器、等設計成可修改參數的模塊。但是CPLD/FPGA的規模越來越大,設計越來越復雜,所以設計者的任務難度大大的提升了。但是調用IP核能避免重復勞動,減輕工程師的負擔,因此使用IP核是能夠縮短大量產品上市時間。

利用IP核設計電子系統,引用方便,修改基本元件的功能容易。具有復雜功能和商業價值的IP核一般具有知識產權,盡管IP核的市場活動還不規范,但是仍有許多公司從事IP核的設計、開發和營銷工作。

IP核有三種不同的存在形式,分別對應我們常說的三類IP內核:軟核、固核和硬核。這種分類主要依據產品交付的方式,而這三種IP內核實現方法也各具特色。

固核是和硬核的折衷。大多數應用于FPGA的IP內核均為軟核,軟核有助于用戶調節參數并增強可復用性。軟核通常以加密形式提供,這樣實際的 RTL對用戶是不可見的,但布局和布線靈活。在這些加密的軟核中,如果對進行了參數化,那么用戶就可通過頭文件或圖形(GUI)方便地對參數進行操作。對于那些對時序要求嚴格的內核(如接口內核),可預布線特定信號或分配特定的布線資源,以滿足時序要求。這些內核可歸類為固核,由于內核是預先設計的代碼模塊,因此這有可能影響包含該內核的整體設計。由于內核的建立、保持時間和握手信號都可能是固定的,因此其它電路的設計時都必須考慮與該內核進行正確地接口。如果內核具有固定布局或部分固定的布局,那么這還將影響其它電路的布局。

PCIE DMA控制器在發送和接收數據時需要嚴格按照PCIE協議進行組包和拆包,同時由于每次DMA傳輸的數據量等傳輸參數不盡相同,還需要設計DMA狀態控制模塊,配置與DMA操作相關的寄存器。此外,還需要實現DDR3到PCIE DMA控制器的接口轉換模塊和DDR3控制器。

發送引擎主要負責將待發送數據按照PCIE協議組織成不同類型的TLP數據包,并發送給PCIE IP核;發送DMA控制模塊主要負責把DDR3中讀取的數據轉換成TLP格式,并傳送給發送引擎;接收引擎用于從PCIE IP核接收不同類型的TLP數據,接收DMA控制模塊用于實現存儲器讀請求包的發送流量控制及接收數據位寬的轉換;DMA狀態控制寄存器模塊主要用來解析來自PC對模塊內部寄存器的命令和配置,并通知發送引擎模塊、接收引擎模塊及其他模塊作出相應執行。

以上就是IP核的介紹,想要學習更多內容的同學可以加蘭老師微信了解。

溫馨提示:明德揚擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 前端模擬采集、射頻、電荷靈敏前置放大器

有相關需求可以聯系:蘭老師18011939283(微信同號)