LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應用的新型技術。由于其可使系統供電電壓低至 2V,因此它還能滿足未來應用的需要。此技術基于ANSI/TIA/EIA-644 LVDS 接口標準。LVDS 技術擁有 330mV 的低壓差分信號 (250mV MIN and 450mV MAX) 和快速過渡時間。 這可以讓產品達到自 100 Mbps 至超過 1 Gbps 的高數據速率。此外,這種低壓擺幅可以降低功耗消散,同時具備差分傳輸的優點。

由多個數據位和時鐘組成的源同步接口已成為電子系統中移動圖像數據的一種常用方法。比較流行的標準是7:1LVDS接口(用于通道鏈路、平面鏈路和攝像機鏈路),它已經成為許多電子產品的通用標準,包括消費設備、工業控制、醫療和汽車遠程信息處理。在這些應用中,使用低成本FPGA進行圖像處理的做法已經變得相當普遍。

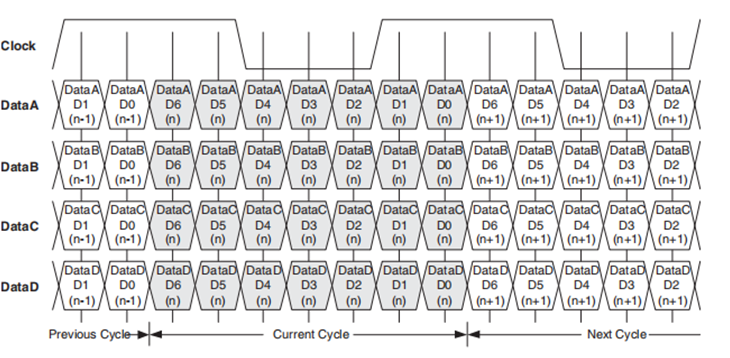

7:1 LVDS接口是一個源同步LVDS接口。如圖1所示,為低速時鐘的每個周期序列化7個數據位。通常,接口由四個(三個數據,一個時鐘)或五個(四個數據,一個時鐘)LVDS差分對組成。四對轉換為21個并行數據位,五對轉換為28個并行數據位。注意,在時鐘上升沿和字邊界之間有一個2位偏移。每個字節有7位長。

每個通道包括一個串行LVDS數據對和一個源同步LVDS時鐘對。接收方接收到該串行LVDS數據,對其進行反序列化,并將其對齊到原始單詞邊界,生成7個并行LVTTL數據位。7:1發送器將7個LVTTL并行數據位串行化為一個LVDS數據位,并將該串行數據通道與LVDS時鐘一起傳輸。

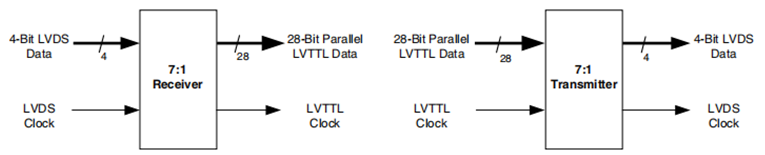

圖2顯示7:1接收方接收4個LVDS數據通道。當反序列化時,它生成28位寬的并行數據。類似地,7:1發送器序列化28位并行數據,生成4個LVDS數據通道。

基于FPGA的通道鏈接和平面鏈接樣式接口的需求包括四個關鍵組件:高速LVDS緩沖區、用于生成反序列化時鐘的鎖相環、輸入數據捕獲和傳動裝置以及數據格式化。數據和時鐘以LVDS格式接收或發送到FPGA或從FPGA發送,數據速度相對較快。準確的速度取決于分辨率、幀速率和顯示器使用的顏色深度。例如,800x600到1024x768顯示器要求LVDS數據在60 Hz到75 Hz的刷新率下從40 MHz傳輸到78.5 MHz。這意味著LVDS的數據速率為280 Mbps到549 Mbps。更高分辨率的顯示器,如1280x1024 60 Hz,則需要使用108 MHz LVDS時鐘傳輸數據。對于這個系統,數據傳輸速率為756mbps。

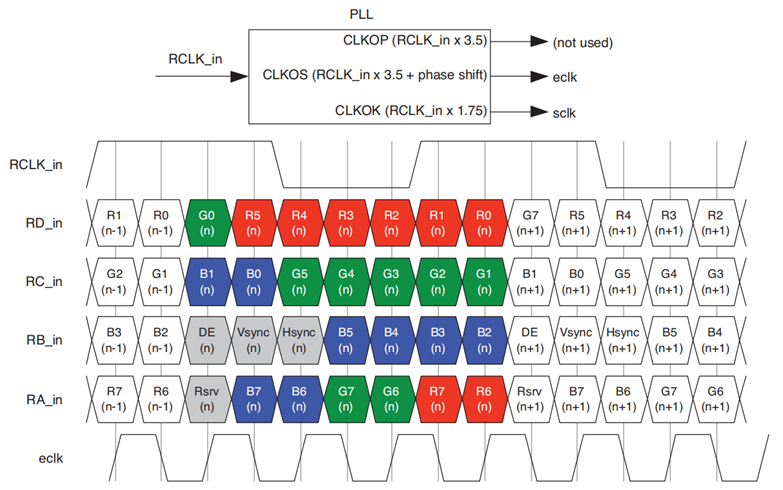

在LATTICE ecp3、LATTICE ecp2 /M或LATTICE exp2實現中,輸入捕獲電路使用雙數據速率(DDR)寄存器,在時鐘的上升和下降沿捕獲數據。當作為接收器工作時,所提供的低速時鐘必須乘以3.5倍,以便在兩個時鐘邊緣捕獲數據。如果輸入捕獲電路只在時鐘的一側工作,則必須使用7的倍數。

理論上可以有這么一種替代方案:可以通過生成7個相移形式的低速時鐘,并使用7個不同的寄存器捕獲輸入數據。然而,時鐘生成和分發的挑戰使得這種方法在FPGA實現中難以應用。低速時鐘必須具有相對較低的抖動,因為它的抖動必須在總體定時預算中考慮。類似地,用于將時鐘提供給輸入或輸出寄存器的時鐘分布網絡偏差必須在任何時序分析中考慮在內。

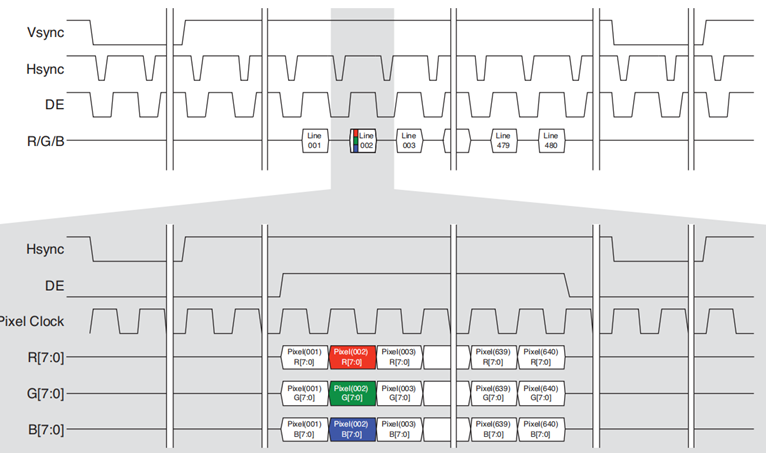

為了傳輸高速數據,發射機必須將用于傳輸低速并行數據的時鐘倍頻3.5倍(在DDR模式下)。同樣,時鐘的抖動及其分布的偏差也很重要,因為它們影響接口的時間預算。圖3顯示了鎖相環時鐘的生成,以及如何將視頻幀第2行的一個像素的R、G、B位、Vsync、Hsync和DE分配給4個LVDS數據對。數據位在eclk時鐘上升和下降的邊緣上采樣。

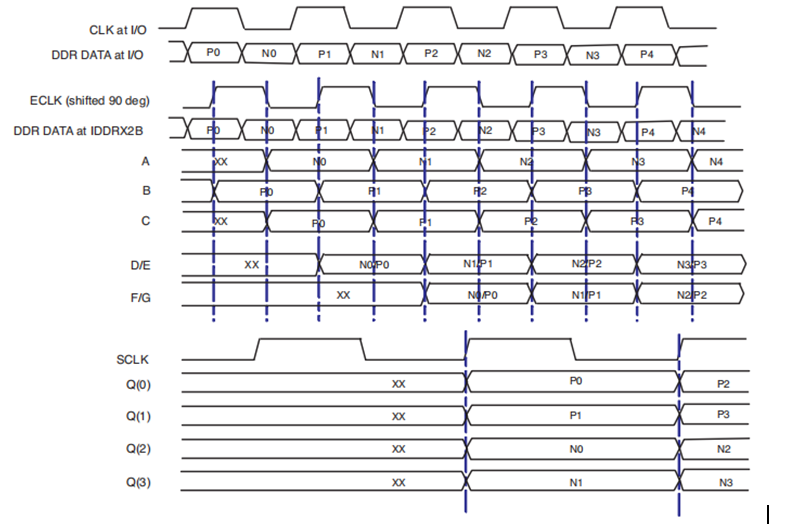

輸入端雙數據速率采樣如圖4:

明德揚的LVDS視頻開發項目使用的便是這種模式,內部eclk是輸入時鐘的3.5倍頻時鐘,中間經過解串、RGB映射后與攝像頭采集的數據進行拼接,最后再將并行數據轉換為串行數據輸出。

溫馨提示:明德揚擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 前端模擬采集、射頻、電荷靈敏前置放大器

有相關需求可以聯系:蘭老師18011939283(微信同號)