本文以一個案例的形式來介紹lattice DDR3 IP核的生成及調用過程,同時介紹各個接口信號的功能作用:

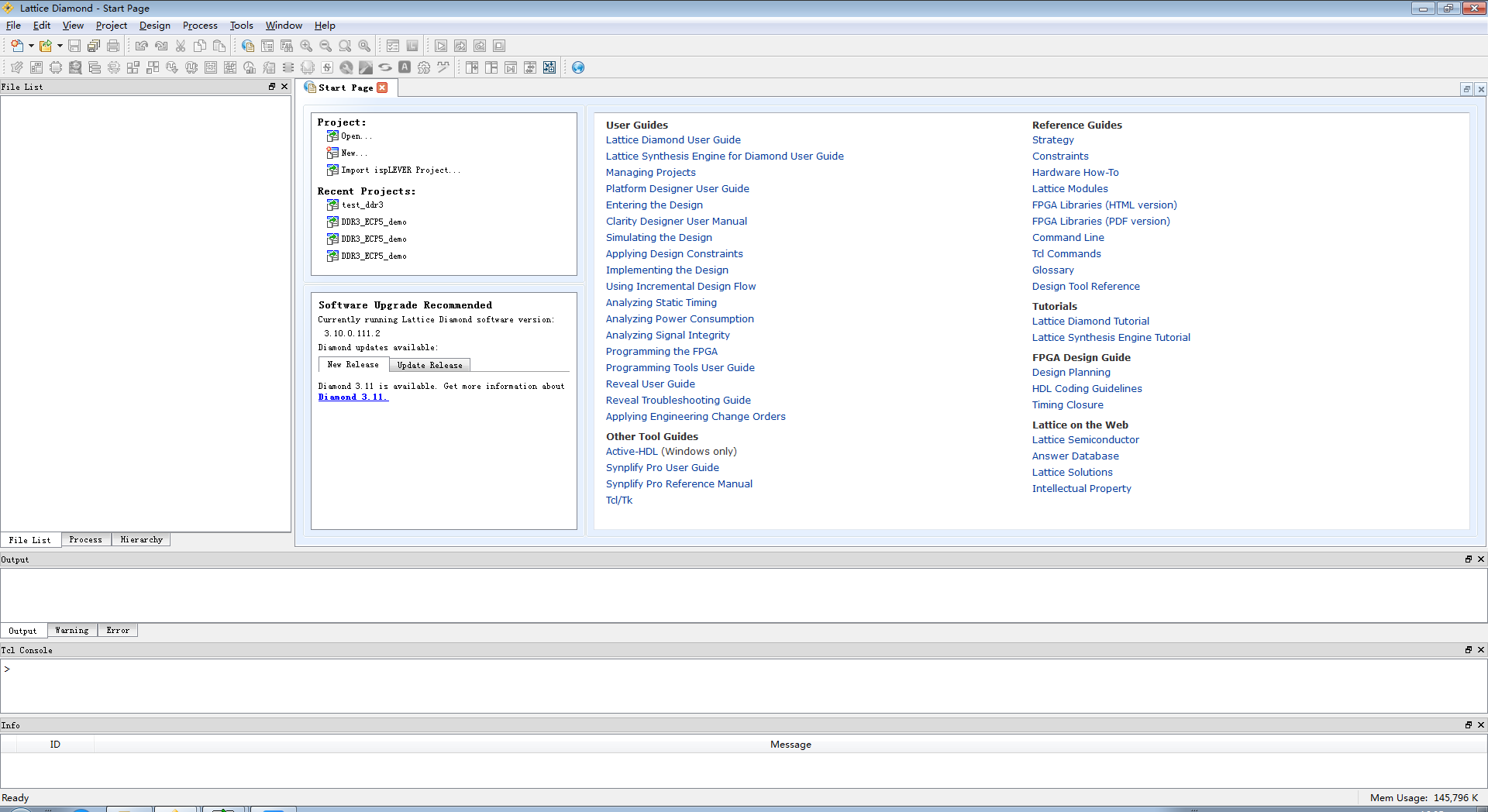

一、建立Lattice工程

1、首先,新建一個工程“lattice_ddr3”:

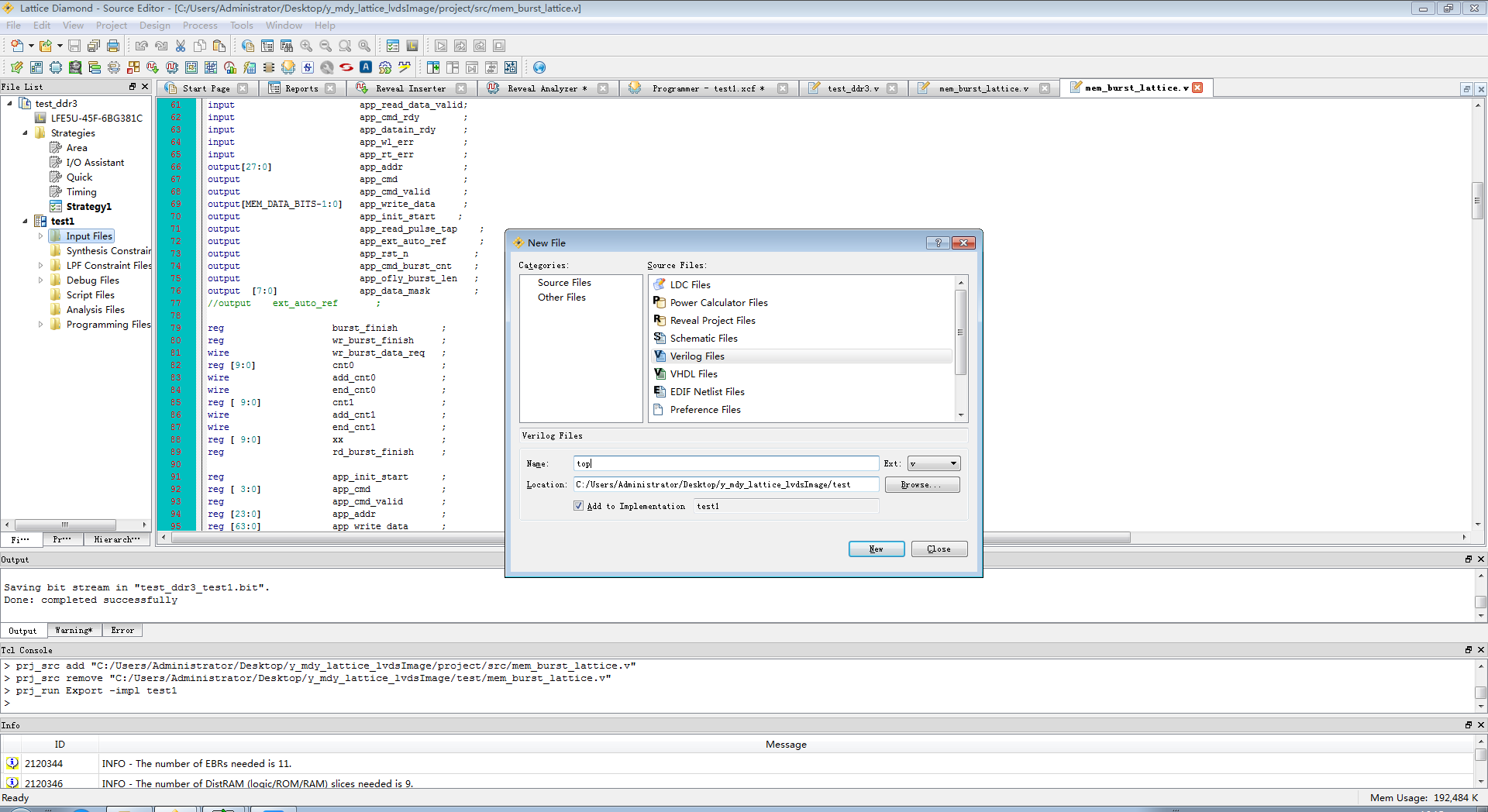

其中器件選擇的是ECP5U系列LFE5U-45F-CABGA381芯片,Lattice的工程后綴是.ldf文件。進入工程界面后,添加模塊文件:右鍵點擊Input Files --Add--New File--Verilog Files即可添加。

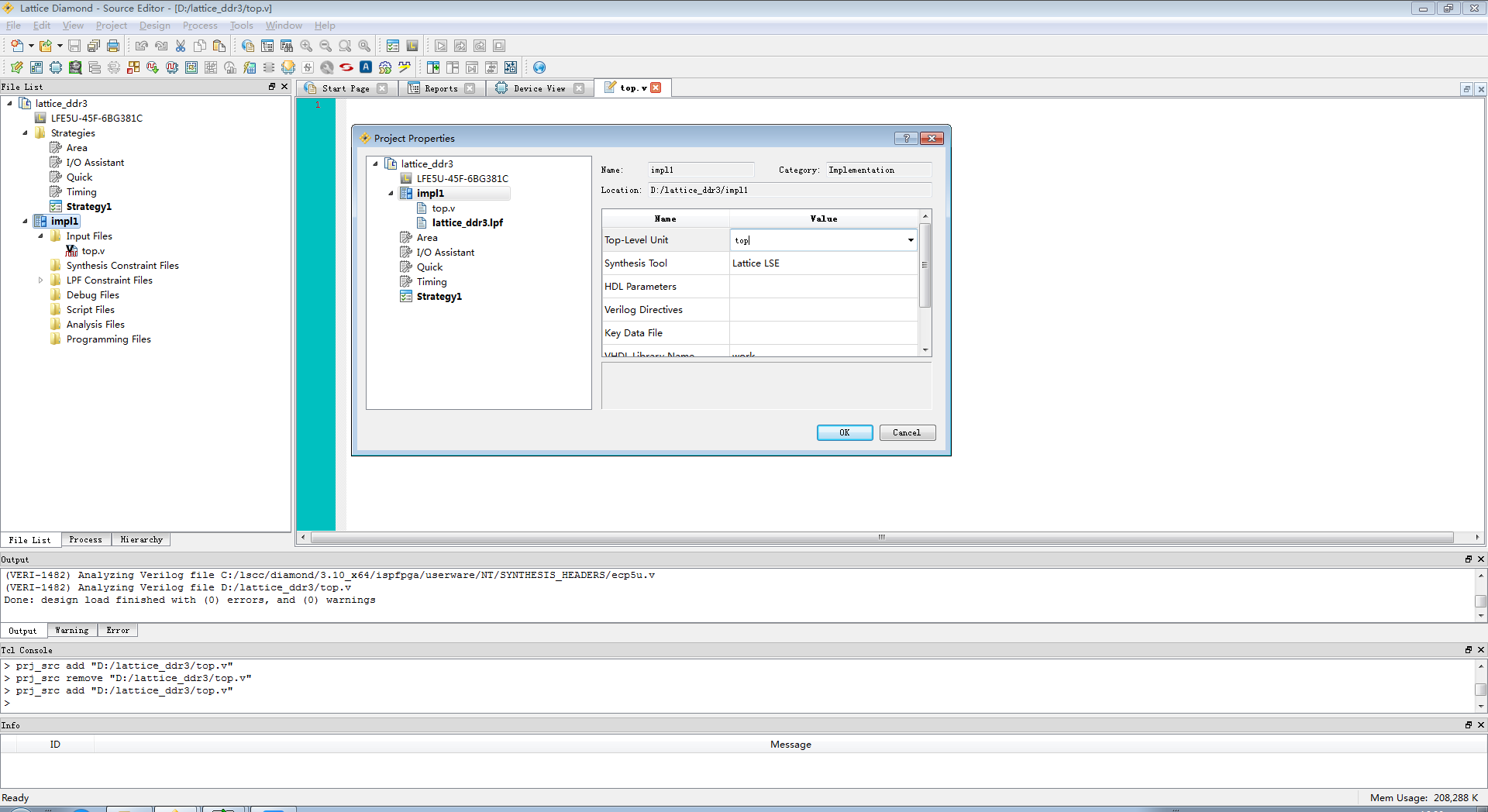

2、添加了工程文件后,需要設置一個頂層,右鍵點擊impl1,選擇Set Top-Level unit,在彈出的窗口中設置頂層文件的名稱,綜合軟件選擇系統自帶的Lattice LSE。

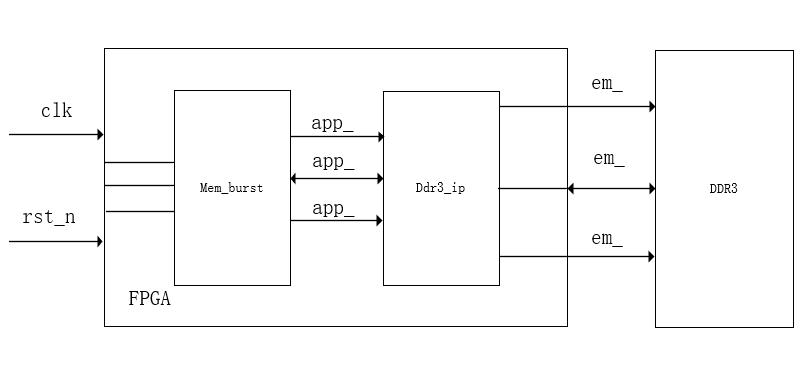

二、頂層文件設計

其中,IP核控制模塊Mem_burst中是雙端口的輸入輸出,輸入信號有頂層中產生的輸入和IP核返回的輸入信號;輸出有IP核輸出到Mem_burst的信號和控制模塊輸出到頂層的信號。

三、模塊信號功能介紹:

DDR3 IP核的調用主要有兩部分模塊,分別是控制模塊和IP核接口模塊,其對應的各信號列表如下:

1、控制模塊的信號功能列表如下所示:

2、DDR3 IP核的接口信號功能列表如下:

四、DDR3 IP核生成過程:

在例化DDR3的IP核之前,需要先生成DDR3的IP核,且DDR3的例化與其他IP核不同,具體的過程如下:

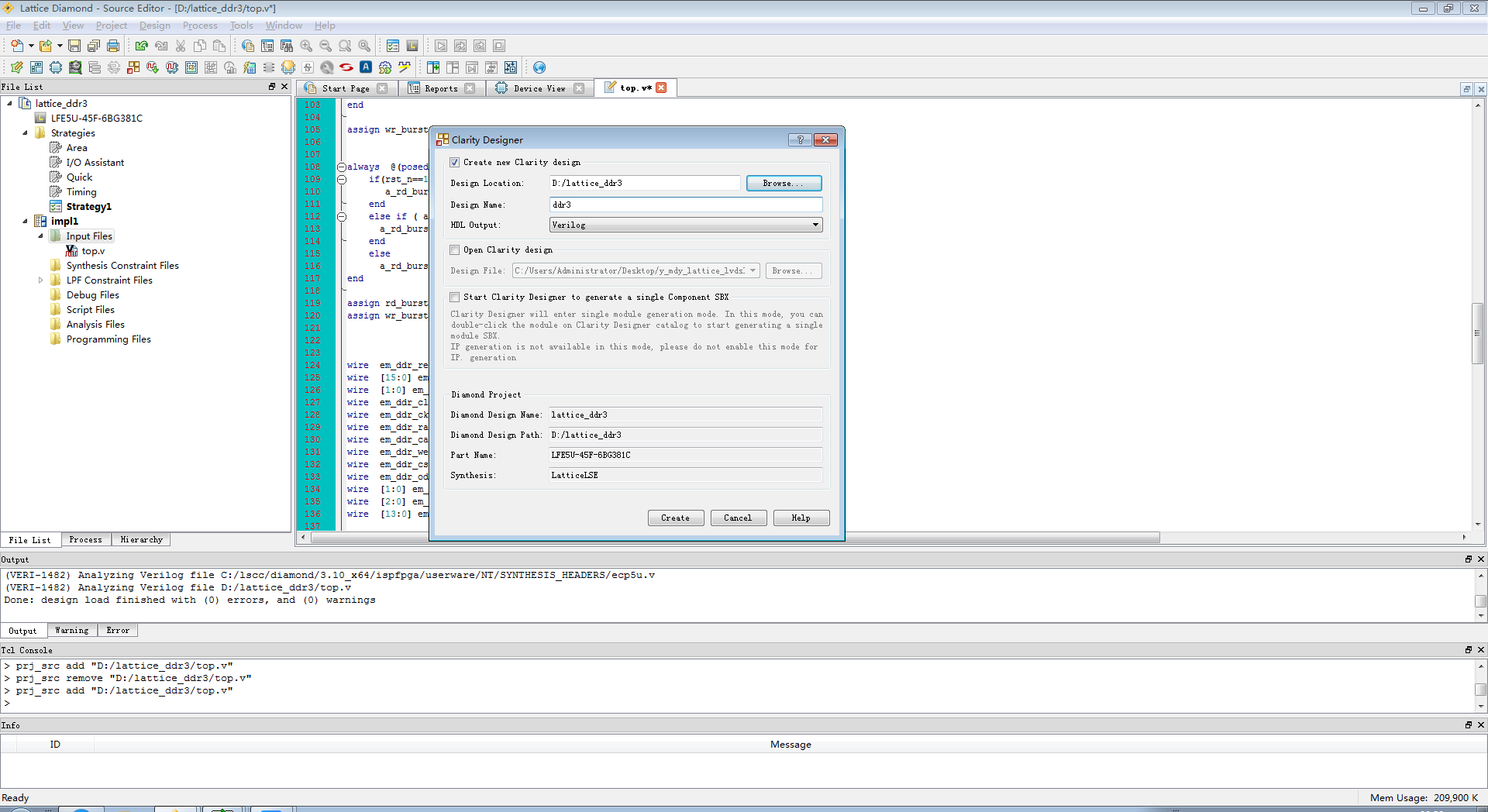

1、首先打開Clarity Designer創建一個IP文件:

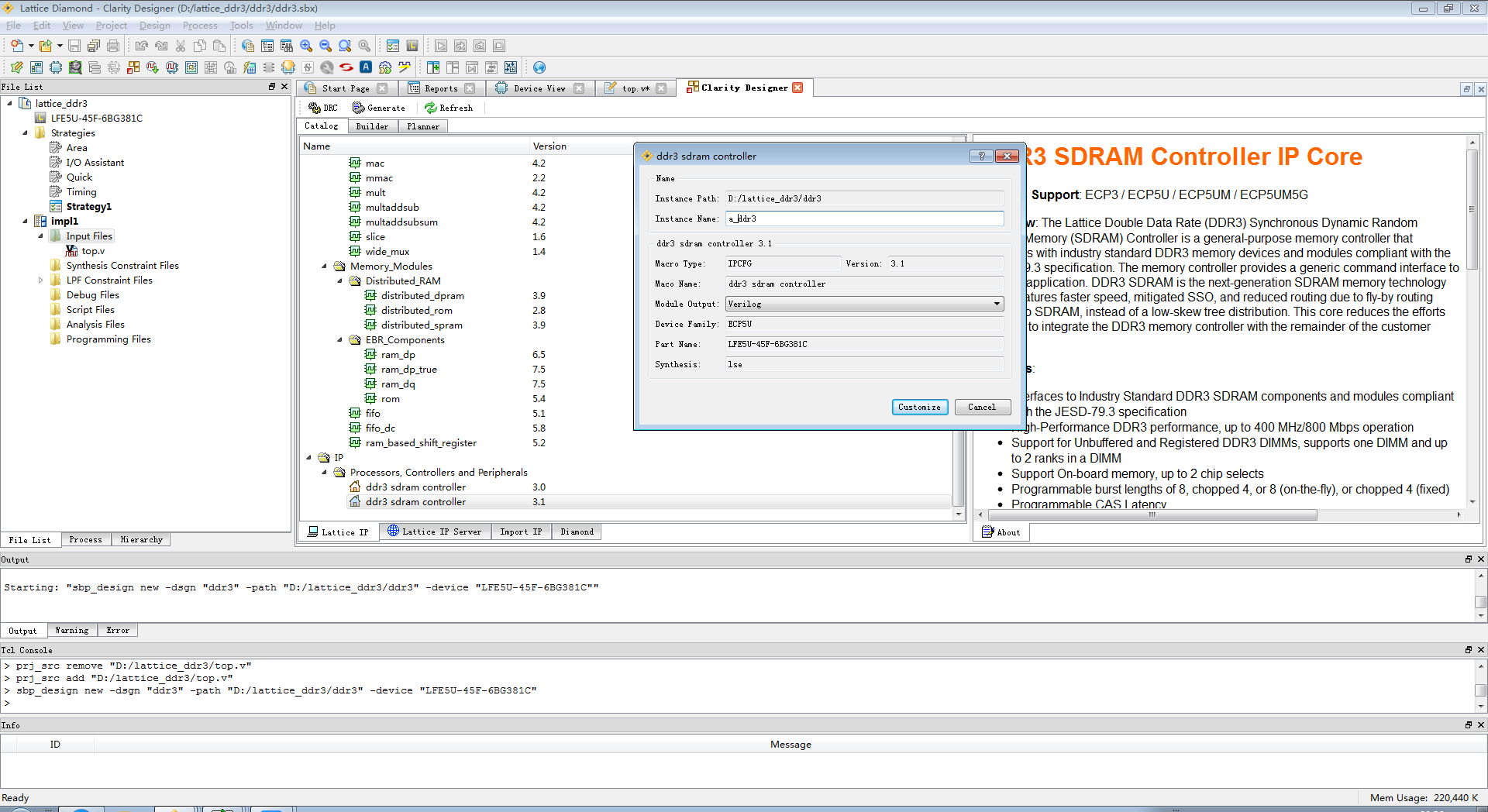

2、進入IP核生成界面后,需要在網上下載DDR3的IP核,在Lattice IP Sever中進行聯網下載DDR3的IP核并安裝,安裝完IP核后在Lattice IP中選擇ddr3 sdram controller 3.1,進行IP核參數設計:

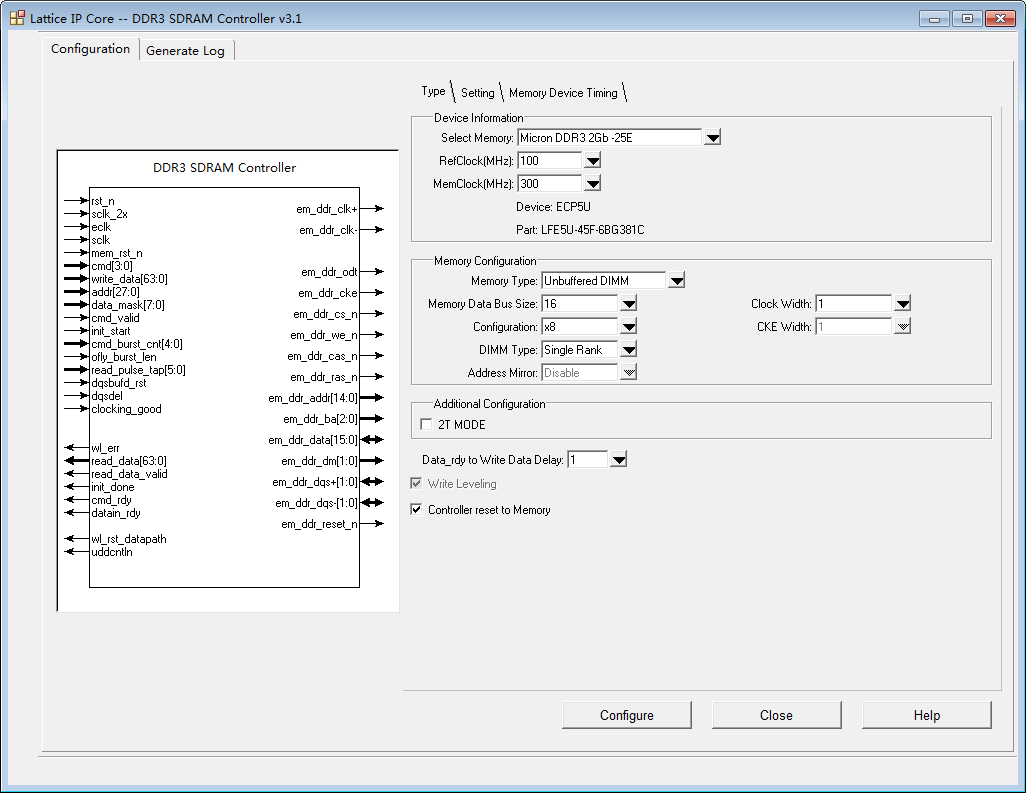

3、配置IP核參數,由于選取的器件是ECP5U系列FPGA,因此DDR3的頻率需設置為300M,否則生成的IP核是灰色的無法加入工程中去,內存數據總線大小選擇16,對應的輸入數據位寬是64位,配置選擇X8,對應的地址位寬是28位。

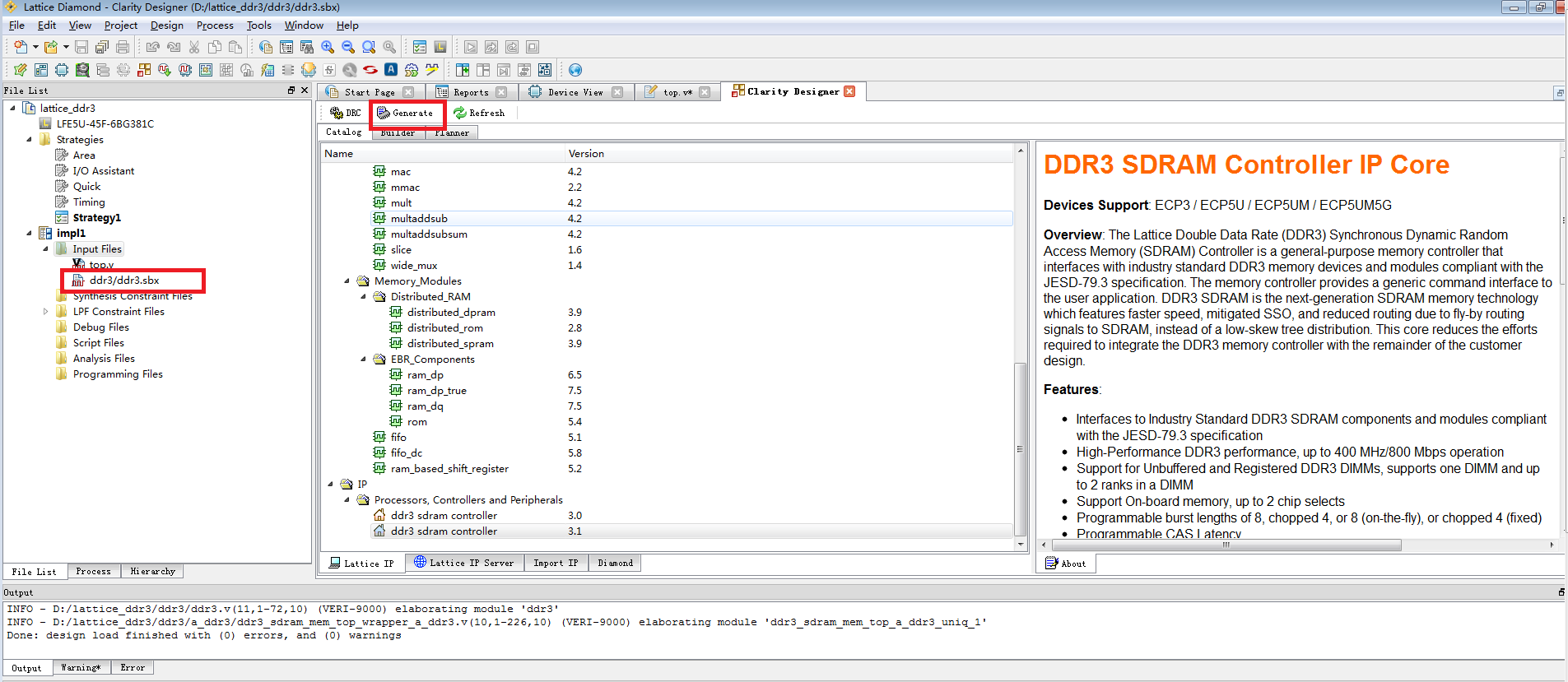

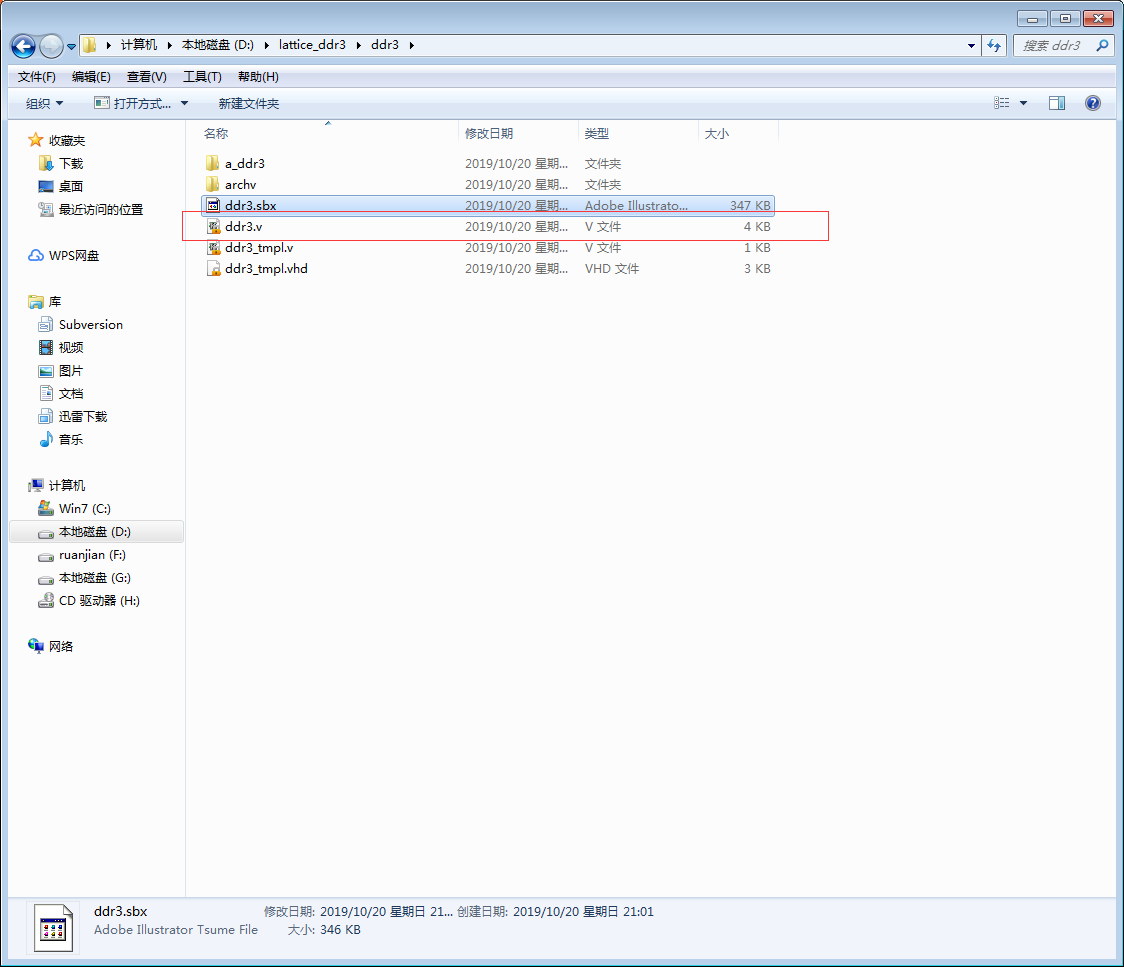

4、IP核生成完成后,點擊系統IP核界面上Generate,會在工程的文件列表中加入一個.sbx文件,此文件就是需要例化的DDR3 IP核實體文件,同時在對應的文件夾下面會出現一個對應名稱的.V文件,將這個.V文件中的信號例化進頂層中即可。

5、需要例化的.V文件:

五、例化IP核

將上圖中的.V文件例化進頂層文件中,定義好信號類型,將對應的信號相連接。至此,DDR3的IP核添加成功。

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://m.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯系易老師:13112063618(微信同步)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)

本文TAG: