1、概述

基于明德?lián)P至簡(jiǎn)設(shè)計(jì)法和明德?lián)P設(shè)計(jì)規(guī)范,設(shè)計(jì)一個(gè)基于FPGA的頻率、電壓測(cè)量?jī)x器,實(shí)現(xiàn)了測(cè)量AD采集后的波形頻率和電壓(峰峰值),并將數(shù)值顯示在數(shù)碼管上。這個(gè)案例通過擴(kuò)展還可結(jié)合明德?lián)P的波形采集顯示案例實(shí)現(xiàn)顯示波形頻率、峰峰值功能,還可拓展結(jié)合上次DDS案例產(chǎn)生的已知波形的頻率峰峰值,驗(yàn)證本設(shè)計(jì)的正確性。

本案例的擴(kuò)展和應(yīng)用在現(xiàn)實(shí)生活中具有重大意義。

在本案例的設(shè)計(jì)過程中,應(yīng)用了至簡(jiǎn)設(shè)計(jì)法、狀態(tài)機(jī)模板應(yīng)用等,在經(jīng)過逐步改進(jìn)、調(diào)試等一系列工作之后,最終達(dá)到了設(shè)計(jì)目標(biāo)。

2、設(shè)計(jì)目標(biāo)

(1)將AD采集后的數(shù)據(jù)轉(zhuǎn)換成同頻率的方波,并測(cè)量出波形實(shí)際頻率

(2)能夠?qū)崿F(xiàn)測(cè)量出波形的周期

(3)能夠?qū)崿F(xiàn)測(cè)量波形的峰峰值或者某個(gè)信號(hào)的電壓值

(4)數(shù)碼管顯示頻率或電壓值,并通過按鍵控制切換決定數(shù)碼管顯示頻率或電壓值

3、模塊功能

(1)頻率測(cè)量模塊實(shí)現(xiàn)功能:

將AD采集后的數(shù)據(jù)轉(zhuǎn)換成同頻率的方波;

測(cè)量出波形的實(shí)際頻率;

測(cè)量出波形的周期

(2)電壓測(cè)量模塊實(shí)現(xiàn)功能:

將AD采集后的數(shù)據(jù)進(jìn)行緩沖;

記錄數(shù)據(jù)最大值和最小值;

根據(jù)公式得出波形的峰峰值(電壓)

(3)數(shù)碼管顯示模塊實(shí)現(xiàn)功能

數(shù)碼管顯示頻率值或者電壓值

通過按鍵1實(shí)現(xiàn)切換決定數(shù)碼管顯示頻率還是電壓

(4)按鍵模塊實(shí)現(xiàn)功能:

將外來異步信號(hào)打兩拍處理,將異步信號(hào)同步化;

實(shí)現(xiàn)20ms按鍵消抖功能,并輸出有效按鍵信號(hào);

4、信號(hào)定義

(1)頂層模塊Freq_Volt_Top.v

信號(hào) | 定義 |

clk | 系統(tǒng)時(shí)鐘 |

rst_n | 低電平復(fù)位信號(hào) |

ad_data | AD采集輸入 |

seg_sel | 數(shù)碼管位選信號(hào) |

Seg_ment | 數(shù)碼管顯示信號(hào) |

(2)頻率測(cè)量模塊Frequency.v

信號(hào) | 定義 |

clk | 系統(tǒng)時(shí)鐘 |

rst_n | 低電平復(fù)位信號(hào) |

ad_data | AD采集輸入 |

Freq | 頻率值 |

Period | 周期 |

(3)電壓測(cè)量模塊Voltage.v

信號(hào) | 定義 |

clk | 系統(tǒng)時(shí)鐘 |

rst_n | 低電平復(fù)位信號(hào) |

ad_data | AD采集輸入 |

Volt | 電壓值(峰峰值) |

(4)數(shù)碼管顯示模塊sel_disp.v

信號(hào) | 定義 |

clk | 系統(tǒng)時(shí)鐘 |

rst_n | 低電平復(fù)位信號(hào) |

din | 顯示數(shù)據(jù) |

seg_sel | 數(shù)碼管位選信號(hào) |

Seg_ment | 數(shù)碼管顯示信號(hào) |

(5)按鍵模塊key_module.v

信號(hào) | 定義 |

clk | 系統(tǒng)時(shí)鐘 |

rst_n | 低電平復(fù)位信號(hào) |

key_in | 按鍵輸入 |

key_vld | 有效按鍵 |

5、頻率測(cè)量代碼

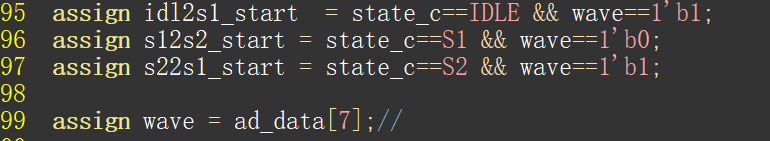

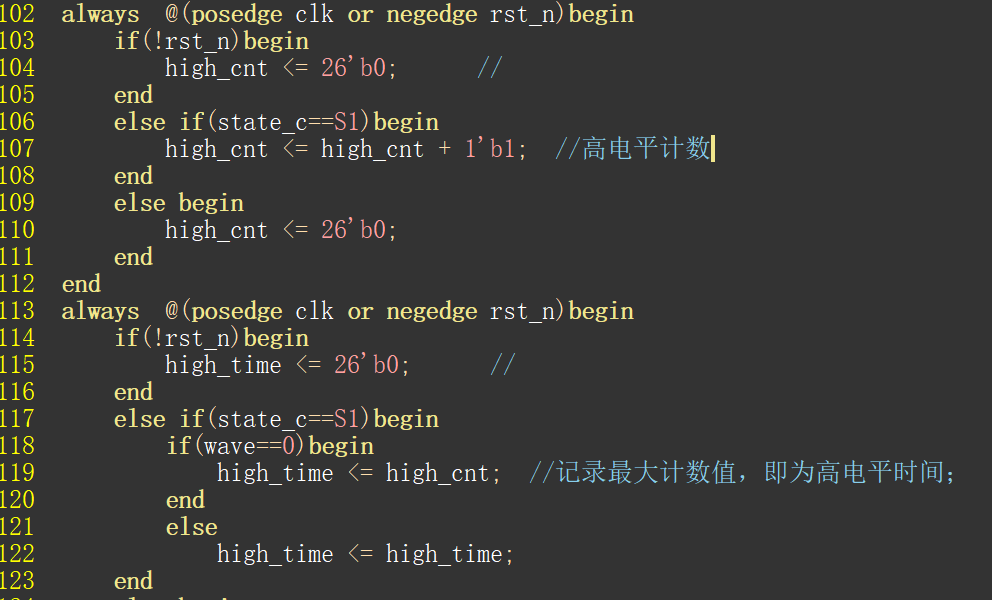

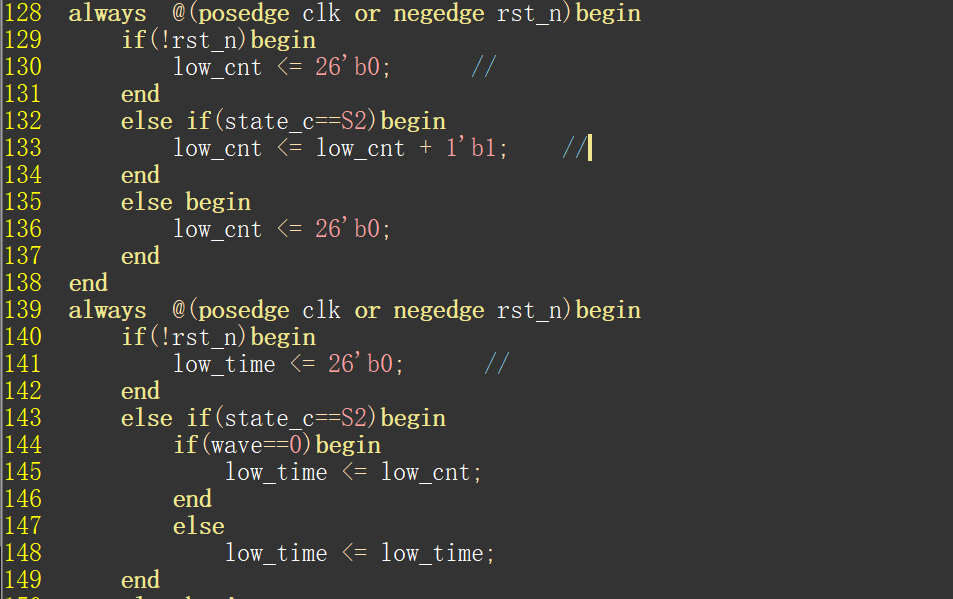

利用明德?lián)P的四段式狀態(tài)機(jī)模板,可以很熟練地寫出狀態(tài)的轉(zhuǎn)換,先將ad_data取最高位,得到同頻率的方波,再分別計(jì)算方波高電平和低電平的時(shí)間,就可以得出一個(gè)周期的時(shí)間,從而計(jì)算出頻率值和峰峰值。利用wave的高低電平控制狀態(tài)機(jī)進(jìn)入高電平計(jì)數(shù)或低電平計(jì)數(shù)狀態(tài)。

S1狀態(tài):即wave=1時(shí)開始進(jìn)行高電平計(jì)數(shù),wave=0時(shí)證明變?yōu)榈碗娖剑涗浵?/span>high_cnt的最大值,代表高電平的時(shí)間。

S2狀態(tài):即wave=0時(shí)開始進(jìn)行低電平計(jì)數(shù),wave=1時(shí)證明變?yōu)楦唠娖剑涗浵?/span>low_cnt的最大值,代表低電平的時(shí)間。

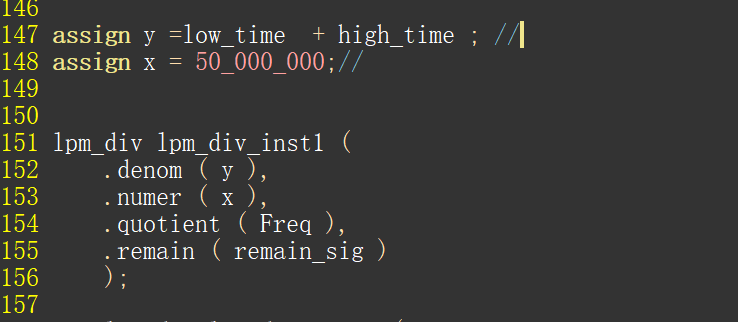

得到高電平和低電平的時(shí)間,相加即得到一個(gè)周期的時(shí)間,可以算出頻率值和周期值

FPGA原則上不能直接進(jìn)行除法運(yùn)算,因此調(diào)用除法器IP進(jìn)行除法運(yùn)算可以算出頻率值,取整數(shù)部分。

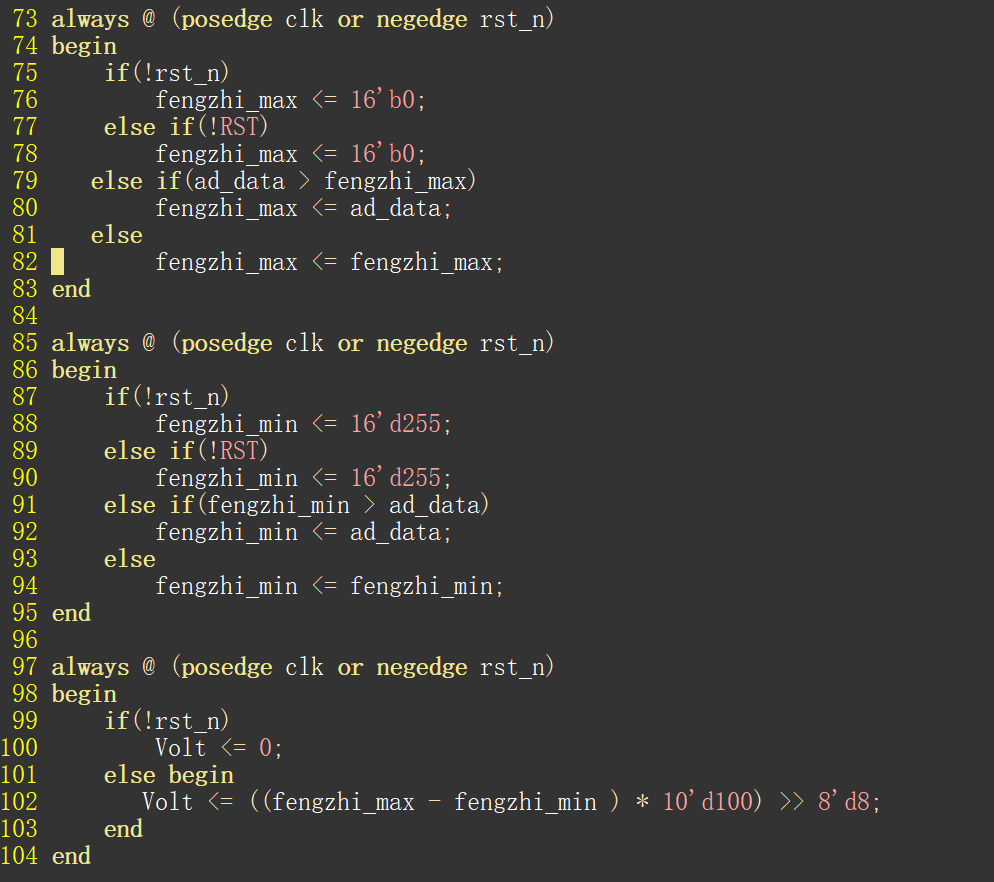

6、電壓測(cè)量

將AD數(shù)據(jù)和初始的最大值最小值相比較,如果AD數(shù)據(jù)大則賦值給fengzhi_max,如果AD數(shù)據(jù)小則賦值給fengzhi_min,經(jīng)過一段時(shí)間后可以得出數(shù)據(jù)的最大值和最小值。如果是8位AD9280,則255代表+5V,0代表-5V;

則可以得到峰峰值計(jì)算公式;

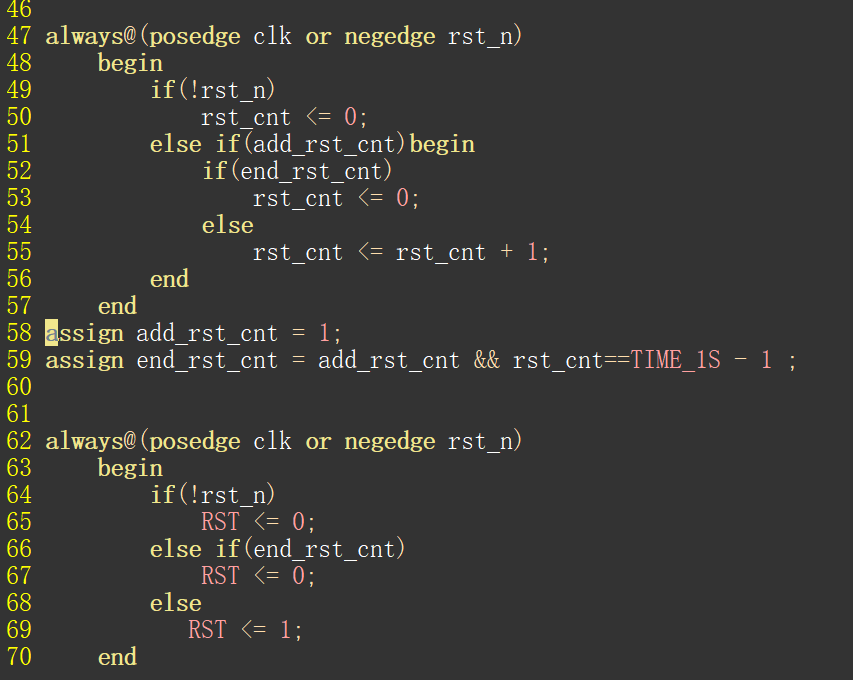

值得注意的是,記錄下最大最小值后,fengzhi_max,fengzhi_min將不變,為了能夠?qū)崟r(shí)記錄數(shù)據(jù)最大最小值,需要定時(shí)刷新,因此設(shè)置1s RST信號(hào),定時(shí)初始化fengzhi_max,fengzhi_min。

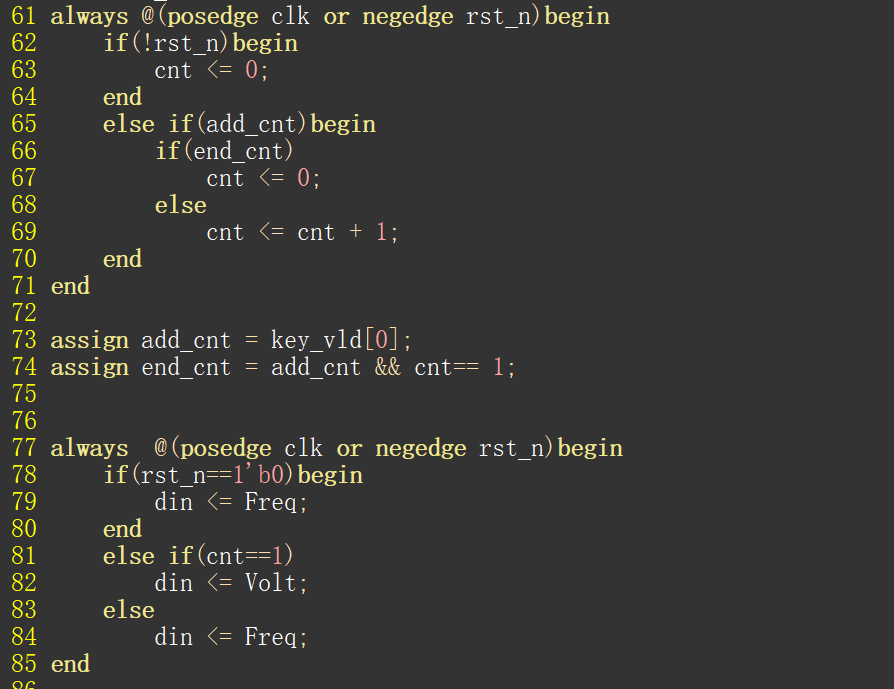

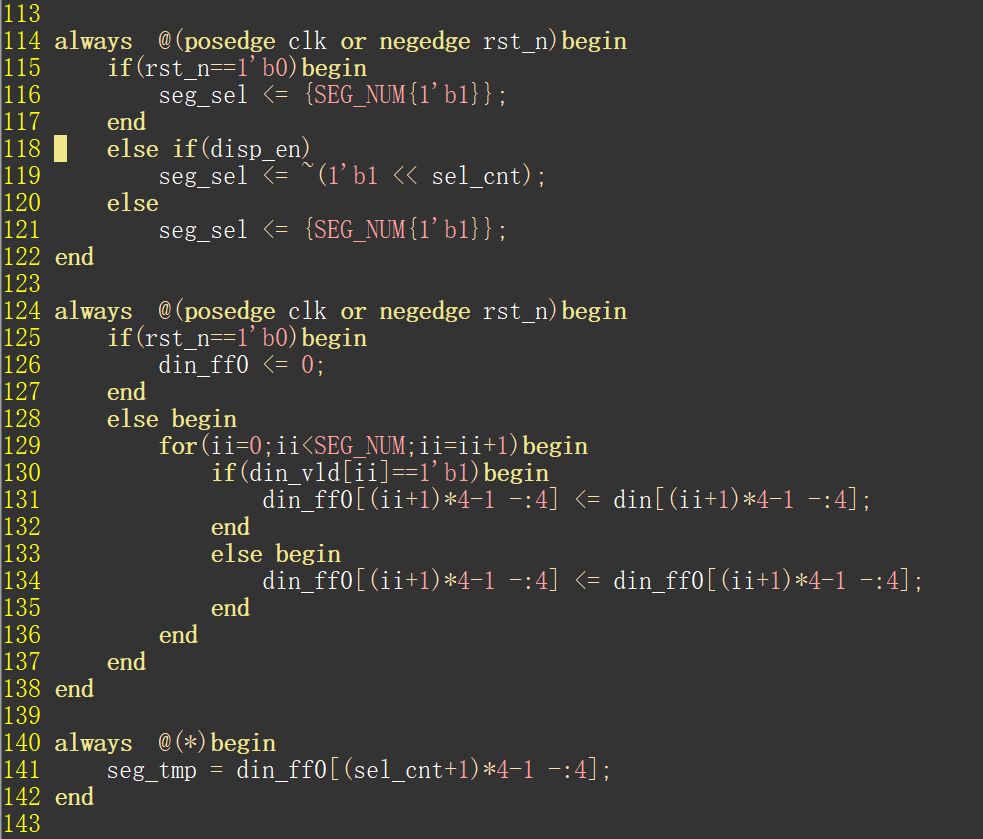

7、數(shù)碼管顯示

通過按鍵切換決定數(shù)碼管顯示頻率值還是電壓值。

動(dòng)態(tài)掃描數(shù)碼管,同時(shí)顯示多個(gè)不同數(shù)字,顯示頻率和電壓信息。數(shù)碼顯示原理和案例具體請(qǐng)學(xué)習(xí)明德?lián)P論壇上資料。

在這個(gè)設(shè)計(jì)案例中,至簡(jiǎn)設(shè)計(jì)法和明德?lián)P計(jì)數(shù)器模板、狀態(tài)機(jī)模板發(fā)揮了至關(guān)重要的作用,使我能夠快速準(zhǔn)確完成設(shè)計(jì)。

本設(shè)計(jì)可以加以拓展:結(jié)合明德?lián)PAD采集波形案例,將計(jì)算出的頻率值、電壓值顯示在VGA屏幕上;

對(duì)于初學(xué)者而言,流水燈太簡(jiǎn)單,復(fù)雜項(xiàng)目又太難,不如嘗試一下這些相對(duì)簡(jiǎn)單而又酷炫的案例,并一步步拓展成大項(xiàng)目。趕緊動(dòng)手嘗試吧。

溫馨提示:明德?lián)P2023推出了全新課程——邏輯設(shè)計(jì)基本功修煉課,降低學(xué)習(xí)FPGA門檻的同時(shí),增加了學(xué)習(xí)的趣味性,并組織了考試贏積分活動(dòng)

http://m.cqqtmy.cn/ffkc/415.html

(點(diǎn)擊→了解課程詳情?)感興趣請(qǐng)聯(lián)系易老師:13112063618(微信同步)