如果同學(xué)們的問題我們帖子里面沒有的請第一時間聯(lián)系我微信同步:易老師13112063618(微信同號)

我們對新問題進行補充!

明德?lián)P最近做了抖音系列短視頻,感興趣可以關(guān)注明德?lián)P抖音號:FPGA技巧分享(87481069842)

內(nèi)容不斷更新!點贊+關(guān)注,學(xué)習(xí)不迷路!

一、SDRAM和DDR專題課

【問題1.1】DDR3那個課程,一般線速率能跑到多少?

答:本課程的DDR3內(nèi)容,是基于XILINX K7芯片,使用的是VIVADO平臺。DDR3的時鐘頻率是800M。用戶側(cè)時鐘是200M。

【問題1.3】 使用DDR3 IP一定需要讀地址FIFO,讀數(shù)據(jù)FIFO,寫地址FIFO,寫數(shù)據(jù)FIFO來先進行數(shù)據(jù)緩存嗎?

答:這個理解是不對的。這里沒有跨時間域的信號傳輸?shù)摹R驗镮P核會產(chǎn)生一個本地時鐘,這個本地時鐘是可以直接采集數(shù)據(jù)的,假設(shè)為clk_ddr_local。用戶可以直接使用clk_ddr_local來往IP核傳輸數(shù)據(jù)。好了,接下來再考慮一個場景:我有一組數(shù)據(jù)A,產(chǎn)生于時鐘域clk;A要寫到DDR,DDR的時鐘域是clk_ddr_local。自然地,A要跟時鐘域到clk_ddr_local,然后才能寫到DDR中,這就需要用到FIFO。接下來考慮另一個場景:我有一組數(shù)據(jù)B,產(chǎn)生于時鐘域clk_ddr_local;B要寫到DDR,DDR的時鐘是clk_ddr_local。由于兩個時鐘域相同,直接寫就好了。(通常來說,這已經(jīng)不屬于DDR的知識了,而是屬于跨時鐘域處理的知識,是FPGA工程師都應(yīng)該知道的概念)。

【問題1.4】用戶邏輯控制DDR3讀寫的程序不是需要自己寫嗎?答:官方一般提供了DDR3的IP核。

答:用戶可以通過DDR3 IP核來進行DDR3芯片的讀寫。但是用戶需要寫邏輯來控制DDR3 IP核。

【問題1.5】課程里會講如何通過DDR3 IP像寫入圖像嗎?

答:課程中的SDRAM部分,會有例子講如何寫入圖像到SDRAM中,DDR3/4也是類似的。但由于每人的項目不同,所以需要學(xué)員根據(jù)自己情況來移植。

【問題1.6】如何知道ddr3里不空,可以讀取了?

答:DDR3和RAM一樣,是一個存儲器件,它的每個內(nèi)部單元都存儲了當(dāng)前的數(shù)據(jù)狀態(tài)值。但DDR3和RAM本身,是沒有“空”、“存有數(shù)據(jù)”,“數(shù)據(jù)滿”等概念的。只要給地址,它就會把當(dāng)前地址的數(shù)據(jù)給到總線上,而且這個地址可以讀很多次。在設(shè)計的時候,是由設(shè)計師用自己寫邏輯來判斷DDR3是否為空。

【問題1.7】請問這個sdram的自動刷新命令發(fā)送后,是不是刷新的是所有bank的同一行都在執(zhí)行刷新呀?也就是說刷新的是不同bank的同一行,是不是這樣理解

答:是的。發(fā)送一個自動刷新命令,所有BANK同一行都會刷新。

【問題1.8】請問有ddr3的IP核手冊嗎?(altera的)

答:IP核不同,界面會所不同,但一般都會提供下載鏈接的。VIVADO、ISE等,也是同樣的情況

【問題1.9】做一個用到ddr4的項目,有一個ddr3的例程,不知道怎么改成ddr4?

答:百度搜索找資料,按流程配置就好,這個我們沒有教程,只能看數(shù)據(jù)手冊

【問題1.10】下圖中的自刷新有啥區(qū)別?

答:上電后,要經(jīng)過初始化,初始化中要有兩次刷新動作;當(dāng)初始化完成后,才是每隔一段時間,要自刷新一次

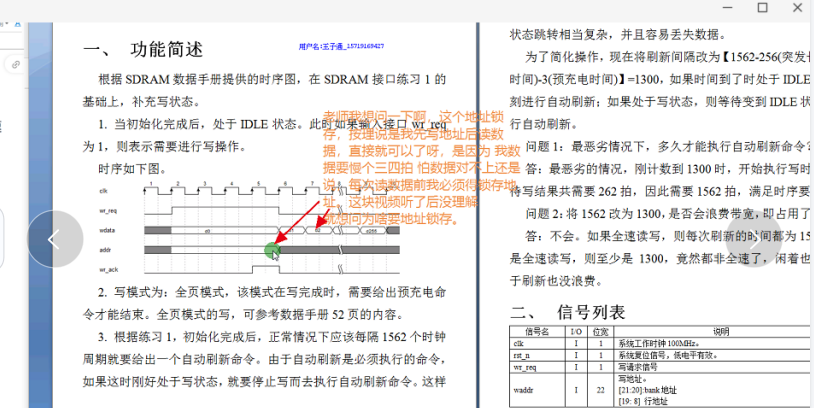

【問題1.11】如下圖所示,為什么在接口中,一般要鎖存住地址addr、寫數(shù)據(jù)wdata等?不鎖存不行嗎?

答:如上圖所示,假設(shè)在第2~6時鐘時刻,addr的值為2,表示此時要寫地址2。本模塊收到此請求后,會在后面如第7~10時鐘,產(chǎn)生寫地址為“2”的時序。但注意,在第7~10,addr的值還是不是2呢?可能不是了。

【問題1.12】請問連接ddr3 ip核與mem_burst時,有些端口未定義。內(nèi)些未定義的端口怎么辦?

答:

1. 本課程提示的案例,經(jīng)過上板驗證是可以的,如果不可以,請及時向老師反映。

2. 本例程驗證過是可以的,因此例化時未連接的信號,就說明對本例程來說不用關(guān)心,不用使用。

3. 如果您要想關(guān)心這些信號,可以閱讀數(shù)據(jù)手冊,了解該信號含義。

【問題1.13】問題:請問老師xilinx FPGA的HR bank的 lvds接口可以驅(qū)動250Mhz DDR adc 嗎?我一直只能跑到100Mhz ,不知道是不是我的時序有問題?

答:

1、首先請確認使用的芯片是否支持該DDR的速率;

2、如果支持的話,請嚴格按照設(shè)計規(guī)范進行設(shè)計;

3、同時請檢查該開發(fā)板的pcb原理圖的設(shè)計是否合適,例如pcb的走線是否等長,或者pcb的板材是否合適、阻抗是否匹配......這些都會影響DDR的速率。

【問題1.14】問題:?有 vivado 下 DDR模型和參數(shù)不?用于仿真?

解答:解答:vivado DDR可以生成對應(yīng)的例程,可以用于仿真。具體操作步驟可以百度搜索一下,例如:Xilinx VIVADO中DDR3 IP核的使用(1)_朽月的博客-CSDN博客_xilinx ddr 自動刷新

【問題1.15】問:SDRAM中將刷新時間改為1300的意義何在?

答:如果以1562個為周期,當(dāng)時間到了之后,如果此時處于寫或讀操作狀態(tài),就要等一段時間再進行刷新操作,這樣刷新間隔就會大于1562,不滿足要求。

【問題1.16】問:請問在邊緣檢測的項目中,輸入輸出數(shù)據(jù)是25M,SDRAM的工作時鐘是100M,這種情況下讀寫效能是多少呀?

答:SDRAM讀寫總線效能一般計算:SDRAM的工作時鐘 * 數(shù)據(jù)位寬 *70% 。(注意:其中70%是指減去sdram的一些操作占用后的效能,70%的數(shù)值是經(jīng)驗之談,請根據(jù)實際情況變更數(shù)值)

【問題1.17】問:SDRAM工程中,讀寫請求是一個脈沖,還是連續(xù)的電平?

答:在MDY自定義的接口中,讀寫請求是一個持續(xù)為高的電平信號,一直拉高直到模塊響應(yīng)為止。拉高一個電平為表示讀寫一次。

二、高手修煉專題課

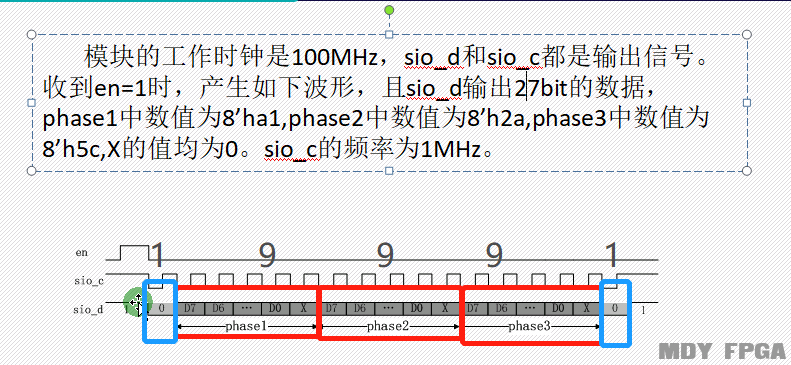

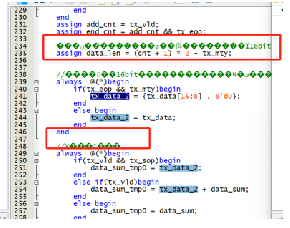

【問題2.1】計數(shù)器練習(xí)的9.4節(jié)中,第二個計數(shù)器的代碼為什么是計30個呀?我認為應(yīng)該是3*(8+1)+2=29個。

答:數(shù)據(jù)位一共是27位,開始位1位,結(jié)束位1位,還要注意看上圖中,第三字節(jié)x后還有1位的0,之后才是結(jié)束位,所以一共是30位。

【問題2.2】在高手修煉課中,使用MDY提供的DO文件跑仿真,提示如下錯誤:

答:這是由于MODELSIM版本不一致導(dǎo)致的。請打開DO文件,去掉下面的-novopt語句。

三、實用調(diào)試技巧專題課

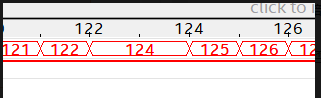

問題【3.1】調(diào)試技巧訓(xùn)練,signaltap練習(xí)1里,我找到了報錯的位置,但是我很好奇為什么會出現(xiàn)這個錯誤:dout沒有輸出123,連續(xù)輸出了兩個124。

答:這是signalTap工具使用的訓(xùn)練習(xí)題,只需要找到錯誤即可,不用修正錯誤。并且該練習(xí)的設(shè)計文件已經(jīng)封裝成IP核了,

無法看到內(nèi)部設(shè)計文件,所以不需要糾結(jié)練習(xí)問題的生成原因。

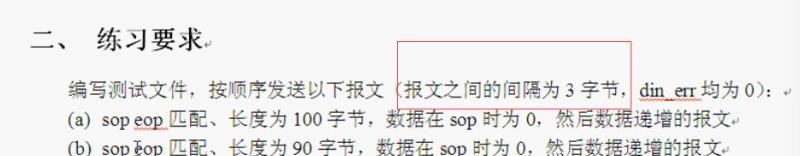

問題【3.2】調(diào)試技巧課程 - 測試文件編寫練習(xí)3-練習(xí)要求中的”報文之間的間隔位3字節(jié)“ 是指3個時鐘周期?

解答:需要根據(jù)報文數(shù)據(jù)的位寬來確定的。例如,報文數(shù)據(jù)data位寬為8bits,那么間隔3字節(jié)就需要3個時鐘周期;假如data是其他位寬,以此類推。

四、FIFO架構(gòu)設(shè)計專題課

【問題4.1】關(guān)于FIFO的深度計算問題?

答:可以看此貼:http://old.mdy-edu.com/jishuwenz/2020/0219/914.html

此答案來自于明德?lián)P的書籍《手把手教你學(xué)FPGA》,電子版可以在此貼下載:http://old.mdy-edu.com/wentijieda/20210410/1324.html

【問題4.2】圖中X代表什么意思

答:這個X是表示并串轉(zhuǎn)換的次數(shù)。FIFO輸出的Q是32位,正常情況下,是有4個字節(jié)的有效數(shù)據(jù),因此x=4。但有一個情況,在包文的最后一個數(shù)據(jù)時,有可能是只有1字節(jié)、或者2字節(jié)、或3字節(jié),或4字節(jié)有效,這個有效多少是取決于mdy的值(經(jīng)過FIFO后,即是Q的33和32位)。可以代入數(shù)據(jù)可以看到x的值。例如:當(dāng)q[33:32]=1時,表示有1字節(jié)無效,即3個字節(jié)有效,所以此時x等于3。

【問題4.3】問:FIFO仿真時,與預(yù)想的不一樣,有時候會出讀出的不對?

答:在做FIFO仿真的時候,如果出現(xiàn)仿真出錯的情況,建議按如下方式定位。 1.一定要抓取FIFO的內(nèi)部信號來觀察。注意,一定是內(nèi)部信號,例如FIFO這個模塊的q、rdreq等。 2.要先確認FIFO的輸入端,即wrreq信號和寫數(shù)據(jù),一個時鐘(寫時鐘)一個時鐘去對,最好記錄一下這個數(shù)據(jù)。 3.其次,確認FIFO的輸出端,即讀時鐘、rdreq和q這三個信號,一個時鐘一個時鐘去對,把數(shù)據(jù)記錄下來。 4.最后,再用寫數(shù)據(jù)和讀數(shù)據(jù)進行對比。另外,一般是不會有問題的,請認真核對。請注意,有部分同學(xué)反饋還是出錯,我們技術(shù)經(jīng)過遠程定位后,發(fā)現(xiàn)同學(xué)在確認數(shù)據(jù)時,沒有按時鐘一個一個來數(shù),導(dǎo)致了疏忽和遺漏,請確保一定要仔細核對。

【問題4.4】wrusedw是寫側(cè)保持數(shù)據(jù)個數(shù), rdusedw是指讀出讀出了多個數(shù)據(jù)個數(shù)?

答:無論wrusedw還是rdusedw,均表示FIFO內(nèi)保存有多少個數(shù)據(jù)。它們之間的區(qū)別僅僅是時鐘域不同,wrusedw對應(yīng)的寫時鐘域,即與寫時鐘對齊的信號;

rdusedw對應(yīng)的是讀時鐘域,即與讀時鐘對應(yīng)的信號。由于寫時鐘和讀時鐘頻率、相位等不同,所以wrusedw和rdusedw是無法完成一致的,使用時要注意。

五、綜合項目實踐課——溫度檢測工程

【問題5.1】溫度控制系統(tǒng):

1.串口進去之后,你有一個ASCII 轉(zhuǎn)Hex的一個模塊 ,然后進去之后有將包頭解析 里面進入控制模塊 可以直接發(fā)送hex數(shù)據(jù) 進入 然后加CRC檢驗

2.原本出來的數(shù)據(jù)是hex數(shù)據(jù)也就是說數(shù)據(jù)出來之后,在上位機去計算一下就好了,反而簡單,在這里你又將HEX轉(zhuǎn)換為ASCII 也就是說 你上去之后又很麻煩,而且下面處理也變麻煩了 。直接發(fā)送hex去上位機解析就好了 。原本一個簡單的小dome最后反而變復(fù)雜了。

3.就是原本溫度的數(shù)據(jù)在采集的過程中 可能會有不穩(wěn)定的情況,你比如在采集的很長的數(shù)據(jù)中,有突變的,但其實,那個是不穩(wěn)定的數(shù)據(jù)。加一個濾波算法進去。這樣數(shù)據(jù)就會很穩(wěn)定。也讓這個小dome變的有意義,因為FPGA主要的就是去做算發(fā) 讓他發(fā)揮他本有的長處,才是最好的做法。

答:

①項目的功能需求各種各樣,當(dāng)然去掉ASCII轉(zhuǎn)換模塊更簡單,但是有的項目它的需求就是ASCII碼操作,所以項目功能的架構(gòu)最終都要根據(jù)需求進行設(shè)計。

②然后,我們這個溫度檢測工程是一個培訓(xùn)項目,所以關(guān)于ASCII功能也會加入到項目中用于訓(xùn)練。

③同時,溫度檢測只是該工程里核心的功能,其他功能的設(shè)計同學(xué)們也可以根據(jù)自己的腦洞想法、自己的需求進行設(shè)計體會,

我們非常歡迎同學(xué)們在群提出和分享自己的思路想法,互相討論,共同進步。

④當(dāng)然同學(xué)們也可以蹲一下我們不定期開播的潘老師直播間,把自己項目功能設(shè)計、架構(gòu)設(shè)計等等的疑問和需求提出來,跟潘老師進行討論,解決你的問題。

【問題5.2】問:在下面的DS18B20的讀時序中,中間部分(即紅色框部分),是否指FPGA要輸出高電平 ?

答:不正確。該時序前面一段是FPGA輸出低電平(dq_out為0,dout_out_en為1)。然后是FPGA釋放總線(dq_out_en為0,dq_out不關(guān)心)。

在后一段,是DS18B20輸出值,F(xiàn)PGA讀出值(dq_out_en為0,dq_out不關(guān)心。取dq_in的值)。

六、綜合項目實踐課——邊緣檢測工程

【問題6.1】點撥開發(fā)板,下載工程檢測工程后,沒有反應(yīng)。

答:注意:下載后,需要按下矩陣鍵盤的按鍵0(即左上角第一個按鍵),才能顯示!!!

【問題6.2】點撥開發(fā)板可以顯示攝像頭拍攝過來的圖片嗎?

答:由于點撥開發(fā)板的資源不足,所以無法顯示攝像頭的圖片,如要顯示,建議購買MP801開發(fā)板。

【問題6.3】PCLK的時鐘頻率問題

答:FPGA提供XCLK給攝像頭,攝像頭利用XCLK產(chǎn)生PCLK。所以PCLK來源于XCLK,所以XCLK是多少,PCLK就是多少。也就是說PCLK和XCLK頻率大小一樣,只是說可能不同相

【問題6.4】是否不使用PLL,而是用PCLK來作為采集模塊的時鐘?

答:PCLK經(jīng)過插件連到FPGA,這其中可能會不穩(wěn)定。為解決此問題,將PCLK連到PLL,產(chǎn)生一個同頻同相的時鐘,使用這個時鐘作為采集模塊的工作時鐘。這樣,即使PCLK缺少或者不穩(wěn)定,但產(chǎn)生的時鐘也會保持穩(wěn)定。

【問題6.5】攝像頭寄存器配置模塊中,配置的是04對應(yīng)RGB,但是數(shù)據(jù)手冊中RGB應(yīng)該是01,這是為什么?

答:這里的Bayer RAW本質(zhì)上是RAW RGB格式,也是RGB格式。RAW RGB:在攝像頭里沒有經(jīng)過任何處理的數(shù)據(jù)。

RGB:在攝像頭里經(jīng)過了ISP等算法處理的數(shù)據(jù)。如果想要最原始的數(shù)據(jù),就使用RAW格式;如果要攝像頭先美化一下,就使用RGB格式。想要哪種格式,取決于您的需求。

【問題6.6】邊緣檢測寄存器是怎么樣配置的呢?

答:邊緣檢測中,ov7670_cfg模塊和sccb模塊,就是用來配置的,可以參考

【問題6.7】邊緣檢查課程案例OV接口是用MIMP還是DVP的?

答:OV7670是標(biāo)準的SCCB接口,兼容IIC接口

【問題6.8】請問在邊緣檢測模塊中的vga_config模塊,如果想顯示完整的一幀圖像(假設(shè)為彩條顯示)而ram資源不夠,我用的多維數(shù)組來做存儲器存儲16bit 640*480個像素點,(目的:在local_wr_req時將寫數(shù)據(jù)按地址存進去,在local_rd_req時將數(shù)據(jù)按地址讀出來),請問以下代碼方案是否可行,若不行,請問該如何實現(xiàn)此目的?(代碼如下圖示)

答:

1. 使用二維數(shù)組代替RAM方法:二維數(shù)據(jù)使用的是寄存器資料,通常RAM資源是遠遠大于寄存器資源的,所以RAM不足時,寄存器一般也不足。

2. 如果只是仿真用途,這個是可以的,可以不考慮資源。既然是仿真,那自然也可以增大RAM了。

3. 注意上面代碼中有錯誤,讀寫地址是獨立,不是共同一個的。讀哪些地址數(shù)據(jù),無關(guān)寫地址。上面代碼中不正確,具體請仿真。

【問題6.9】這個關(guān)系怎么得到的呢?根據(jù)這個圖的話 上面的關(guān)系不應(yīng)該反過來嗎?在下一拍的時候應(yīng)該吧taps0_ff0賦值給taps0x呀?

答:沒有 ff0就是表示 延時一拍的意思,taps0_ff是taps0前一時刻的值,需要得到這種結(jié)果,就是通過時序邏輯打一拍,資料提供的有直播課講解,建議結(jié)合仿真波形去看,測試文件有提供

【問題6.10】請問這一段寫在代碼的哪里?我找不到,看不出

答:在SCCB代碼里

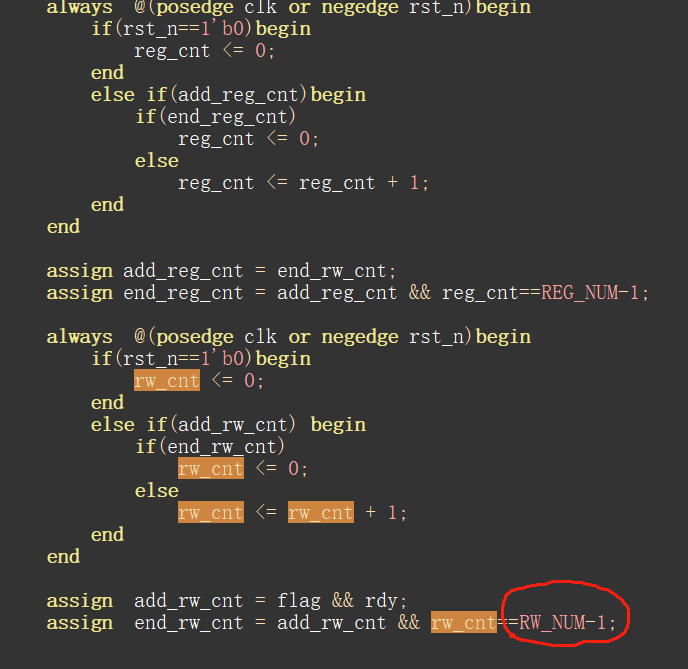

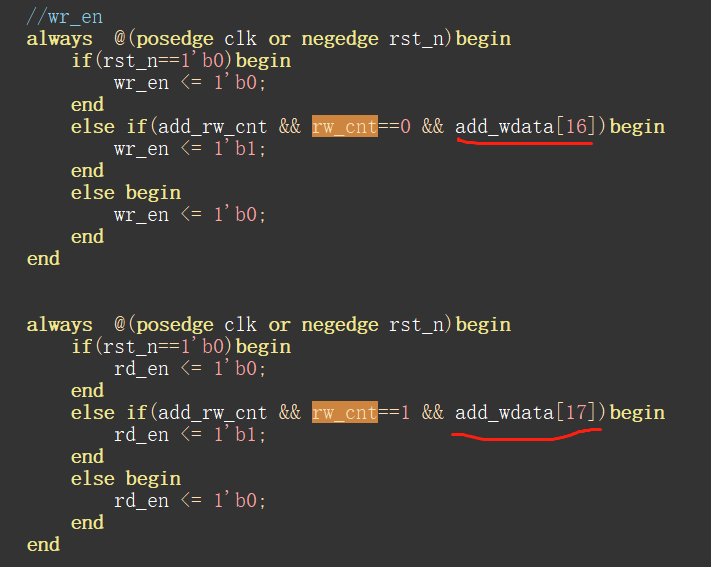

【問題6.11】邊緣檢測課程這個判斷讀或?qū)懯鼓艿挠嫈?shù)器的rw_cnt為什么剛好對應(yīng)add_wdata[16]和add_wdata[17]?

解答:在工作狀態(tài)(flag==1)時,此時對ov7670的指令進行讀寫,那到底是對指令進行讀還是寫,使用讀寫操作計數(shù)器rw_cnt進行計數(shù),按順序的進行判斷。根據(jù)模塊ov7670_para.v 里指令的格式:{讀操作(1bit),寫操作(1bit),操作指令(16bits)}。當(dāng)rw_cnt=0時,設(shè)計上此時先判斷指令寫操作是否有效,因此對應(yīng)判斷ov7670_para.v 里指令的add_wdata[16],確認對應(yīng)比特位的寫操作是否為高電平,如果是,那么需要對該指令進行寫操作,產(chǎn)生一個寫使能有效信號(wr_en==1)。其他以此類推。

【問題6.12】邊緣檢測里面的sccb模塊中,根據(jù)sccb手冊要求,讀時序的傳輸周期要寫成兩段寫,為什么代碼里面省了第二段(設(shè)備地址+讀數(shù)據(jù))?

這上面讀時序傳輸周期只寫了一段。

解答:理解有誤,代碼里sccb的讀操作是有兩段時序的。請聯(lián)系信號 rd_com、count_duan、out_data、flag_sel,直接仿真查看波形一起理解,這樣會更直觀。

【問題6.13】問:邊緣檢測工程中,配置ov7670的寄存器順序是固定,修改順序要重新修改代碼后上電,有沒有辦法可以不上電直接修改?

答:目前代碼就需要重新上電。 不重新上電的方式,就參考溫度檢測工程,需要上位機配合

【問題6.14】問:邊沿檢測課程里,VGA_driver里面的行同步場同步信號為什么需要打拍延時產(chǎn)生?

答:在本模塊中,使用了行計數(shù)器和場計數(shù)器來產(chǎn)生了讀地址rd_addr。

1.該地址送給上游模塊vga_config,然后將數(shù)據(jù)返回給本模塊會有幾個時鐘的延時。

2.為了讓返回的數(shù)據(jù),與最終的信號vga_vys和vga_hys對齊,所以要延時一下,打了兩拍再產(chǎn)生行場同步信號。

3.具體可以通過整體工程仿真來檢查確認。檢查返回的第一個數(shù)據(jù)是否有延時;第一個數(shù)據(jù)與行場同步信號是否有就是對 。

【問題6.15】邊IP核配置代碼中,下面部分的 3'b110,8'h02,32'h00800020 110,02分別屬于什么功能呢

答:

1. 前面3比特的3'b110用于定義讀寫屬性:分別是表示讀、寫和等待位。當(dāng)對應(yīng)位為1,表示使能。

a. 例如,3'b110,表示讀使能、寫使能、等待不使能。那么在代碼中,將會對寄存器先執(zhí)行寫操作,然后再執(zhí)行讀操作。讀操作的目的,是為了檢查寫的對不對。

b.例如,3'b001,表示讀不使能,寫不使能,等級使能。在代碼中,不對寄存器操作,只用于延時。

2. 中間的8位是讀寫地址。即寄存器的地址,對應(yīng)著IP核數(shù)據(jù)手冊中的寄存器地址。

3. 后面的32位是寫數(shù)據(jù)或者延時值。當(dāng)寫寄存器時,是寫到寄存器的數(shù)據(jù)。當(dāng)讀寄存器,不關(guān)心,可填充為0。當(dāng)是延時操作時,表示要延時的值,單位為時鐘周期。

【問題6.16】問:請問邊緣檢測中,對于SDRAM模塊的讀寫,涉及到仲裁內(nèi)容嗎?(邊緣檢測)

答:涉及到,就是讀寫怎么判斷的問題

七、綜合項目實踐課——千兆網(wǎng)項目專題課

【問題7.1】千兆網(wǎng)課程里的udp和百兆網(wǎng)通用的嗎?

答:本課程講述的是千兆網(wǎng),對于百兆網(wǎng)來說,UDP IP MAC和ARP協(xié)議都是相同的,

不同的是MAC IP核、FPGA和PHY芯片的接口不同。 本課程提供的是千兆網(wǎng)的工程,如果要使用百兆網(wǎng),需要根據(jù)上面的內(nèi)容來修改。

【問題7.2】千兆網(wǎng)課程有實現(xiàn)TCP協(xié)議嗎?

答:本千兆網(wǎng)課程實現(xiàn)的是UDP協(xié)議,沒有TCP協(xié)議。

【問題7.3】請問下,三速以太網(wǎng)IP核配置時,32bit對齊選項的意義在哪里?

答:在接口為32bit時,每個VLD有效時的數(shù)量是4個字節(jié)。由于MAC頭是14字節(jié),不是4的整數(shù)倍,在發(fā)送方向,在補上MAC頭后,

必須調(diào)整數(shù)據(jù)(拿出2字節(jié)與MAC頭最后2字節(jié)湊成一個4字節(jié)的有效數(shù)據(jù)),這樣處理比較麻煩。 同時道理,接收方向,去掉14字節(jié)MAC頭后,

會有一個VLD多出2字節(jié)的有效數(shù)據(jù),這樣調(diào)整也麻煩。為此,MAC IP核里有一個功能,就是32位對齊功能。該功能決定,在SOP位置時,

最高2字節(jié)是否為無效數(shù)據(jù)。 當(dāng)是無效數(shù)據(jù)模式時,發(fā)送方向插入2字節(jié)無效數(shù)據(jù)+14字節(jié)MAC頭;在接收方向,刪除前16字節(jié)MAC頭,剩下就是效數(shù)據(jù)。這樣處理就方便很多了。

【問題7.4】 只要勾選了32bit對齊功能,IP核自動添加2字節(jié)的無效數(shù)據(jù)?

答:勾選對齊后,接收方向?qū)h除無效數(shù)據(jù),直接輸出數(shù)據(jù),即SOP位置的高2字節(jié)也是有效的,一直到EOP位置。發(fā)送方向,認為從SOP到EOP的位置都是有效的。

不勾選的話,接收方向,IP核輸出、SOP位置的高2字節(jié)是無效數(shù)據(jù)。發(fā)送方向,進到IP核的數(shù)據(jù)里,將SOP位置的高2字節(jié)視為無效數(shù)據(jù)。

【問題7.5】如下圖所示,當(dāng)使用了PAD_EN功能時,接收方向,會將PAD去掉,但實際上沒有去除,是怎么回事?

答:請看下面描述:第一段,當(dāng)值小于600,該域反映的是長度,才會繼續(xù)檢查PAYLOAD長度,

進而才會有REMOVAL。當(dāng)值大于600時,該域反映的是類型而已,則不會REMOVAL。

【問題7.6】課程里會包含TCP協(xié)議嗎?

答:TCP協(xié)議使用邏輯實現(xiàn)非常復(fù)雜,所以本課程不會包含此部分內(nèi)容。

【問題7.7】RGMII支持10M/100M/1000M三種模式嗎?

答:RGMII是"吉比特介質(zhì)獨立接口"的含義,即1000M的傳輸接口。其他幾種接口包括GMII、MII等。注意一下,10M/100M/1000M三種模式,指的是該“芯片”支持這三種接口,不是說RGMII支持。當(dāng)芯片采用了RGMII或GMII時,就傳輸1000M;當(dāng)采用了MII 100M時,就是傳輸100M。注意的是,RGMII和MII的部分管腳是可以復(fù)用的。

【問題7.8】千兆網(wǎng)配置寄存器的定義代碼中,下面兩個IP核數(shù)據(jù)手冊中沒有說明,是什么作用的?

答:第一行語句的作用是“等待10000個時鐘周期”。目的是當(dāng)完成前面的配置后,等待10000個時鐘后,再去配置下面的寄存器。這是因為有時

候,配置完上面寄存器后,有可能要等一段時間才起作用,所以要等一等。這個“等待”功能是FPGA里面代碼實現(xiàn)的。

第二句作用是測試使用的,可以刪除,在調(diào)試時看看接口是否正確。

【問題7.9】本項目有沒有配置外部的PHY芯片?

答:本項目是沒有配置的,因為默認PHY芯片是不用配置就能正確使用的。

【問題7.10】、百兆網(wǎng)和千兆網(wǎng)的區(qū)別是什么?

答:

1. IP核是一樣的

2. 千兆網(wǎng)使用的是GMII接口,百兆網(wǎng)則是MII接口。gmii數(shù)據(jù)線是8位;MII接口使用是4位數(shù)據(jù)線,也就是TXD低4位和RXD低4位。

3. 時鐘頻率不同,千兆網(wǎng)是125M,百兆網(wǎng)是25M時鐘。

4. 百兆網(wǎng)的TX時鐘來自于PHY芯片,芯片管腳使用的是tx_clk,而不是gtx_clk。

5. MII接口的4位數(shù)據(jù)線,是先發(fā)1個字節(jié)的低4位,再發(fā)高4位。

【問題7.11】老師,咱們千兆網(wǎng)項目中,為啥用sharkwire抓包的時候 最大傳輸速率到不了千兆呢?

答:因為包文傳輸?shù)臅r候,會有消耗的,例如包與包之間有幀間隙,并且每個包會有前導(dǎo)碼和FCS部分。因此達不到理論的千兆。

【問題7.12】請問一下在千兆網(wǎng)工程里,初始化mac IP核時,signaltapii有些reg_cnt剛開始時,add_wdata會出現(xiàn)一小段莫名其妙的數(shù)據(jù),是怎么回事 ?

答:請注意這個signaltap采樣的時鐘一定要跟代碼模塊的時鐘一致。

SignalTap使用教程:http://old.mdy-edu.com/jishuwenz/2019/1210/107.html

【問題7.13】在千兆網(wǎng)的rx_filter模塊中,讀數(shù)據(jù)的時候為什么用add_cnt=m_empty==0,這個信息FIFO的不空作為讀條件?

答:信息FIFO非空,表示數(shù)據(jù)FIFO中存有一個完整的包文,因為需要判斷包文是否正確,所以需要數(shù)據(jù)FIFO中保存一個完整包文之后再讀出。

由于本模塊需要將32位的數(shù)據(jù)轉(zhuǎn)成16位的,計數(shù)器cnt數(shù)兩次,表示數(shù)據(jù)FIFO需要兩個時鐘讀出一次,當(dāng)遇到最后eop的時候,由于可能存在無效字節(jié),所以當(dāng)無效字節(jié)為2個或者3個的時候,計數(shù)器只需要數(shù)一次就夠了。

【問題7.14】在千兆網(wǎng)的rx_filter模塊中,信息FIFO深度為什么設(shè)置為32,設(shè)置為1就可以了吧?

答:這里設(shè)置為32只是順手而為,而且占用的資源也不是很多,所以就沒有進行修改,深度改為1也是可以的。

【問題7.15】在udp發(fā)送的過程中,假設(shè)源端口為0x1234,目的端口為0x5678,那么發(fā)送的是12345678還是56781234?

答:發(fā)送的時候是按照12345678來發(fā)送的

【問題7.16】為什么udp協(xié)議在發(fā)送和接收的時候,源端口和目的端口順序會反?

答:包文的協(xié)議時固定的,只會按照源地址加目的地址的格式發(fā)送。

1.FPGA發(fā)送的時候,F(xiàn)PGA產(chǎn)生包文,端源端口是1234,目的端口是5678。然后發(fā)送格式是源+目,因此發(fā)送的是1234_5678

2.FPGA接收的時候,PC產(chǎn)生包文,源端口是5678,目的是1234,然后發(fā)送的是源+目,因此是5678_1234。

【問題7.17】請問一下,我編譯千兆以太網(wǎng)的時候,為什么把這個clogb2文件添加進去就會報錯,說是sv文件?還有這個文件有什么作用?謝謝

答:clogb2不是一個完整的module文件,它是被用include的方法加入代碼中的。它不需要加到工程上,所以可以把它去掉。

【問題7.18】請問下,在做練習(xí)工程的時候,需要自己設(shè)計MAC首部發(fā)送電路,MAC首部14字節(jié),但數(shù)據(jù)位是4字節(jié)的,我需要定義 發(fā)送首部的計數(shù)器,這里4是不能被14整除的,我應(yīng)該怎么處理?

答:

1、可以在設(shè)計代碼的時,把產(chǎn)生的mac頭、IP頭、UDP頭拼接起來的時候,在最高位補2字節(jié)的無效數(shù)據(jù)零。

2、或者在mac_ip核進行相關(guān)的設(shè)置,具體可以查看相關(guān)數(shù)據(jù)手冊附:數(shù)據(jù)手冊在打開IP核后如圖所示位置查看

【問題7.19】千兆網(wǎng)轉(zhuǎn)百兆網(wǎng)的時候,需要給phy芯片一個參考時鐘,是怎么給的?

答:開發(fā)板上有一個12M的時鐘芯片,是給phy芯片的。外部晶振的事,跟FPGA無關(guān)

【問題7.20】我的采樣時鐘就是模塊的工作時鐘(always塊里的);現(xiàn)在從MAC_IP核輸出的數(shù)據(jù)不正確,根據(jù)常見問題PDF里問題1和6的解答,

有兩種情況,如果時鐘沒問題那就有可能是IP核的輸入信號有問題。我對應(yīng)的代碼和signaltap采集到的數(shù)據(jù)如圖:

請問這種情況下,輸入的數(shù)據(jù)算是正確的嗎?

答:結(jié)果是正確的。原因同上【問題9】

【問題7.21】再設(shè)置好電腦的IP地址之后,把界面關(guān)掉,然后再打開就沒有了,需要重新設(shè)置,怎么解決?

答:

1、點擊左下角的WIN圖標(biāo),輸入CMD然后回車,打開DOS模式窗口。

2、在DOS命令行提示符下直接輸入:“netsh winsock

3、reset”,然后回車,會提示需要重啟,不要管它。

4、在DOS命令行提示符下直接輸入:“netsh int ip reset

5、reset.log”,然后回車,提示重新啟動計算機完成此操作。

6、關(guān)閉DOS窗口,重新啟動計算機,問題解決。

【問題7.22】千兆網(wǎng)我們的和用mdio接口的有什么區(qū)別? 我們的教程是沒有用到這個接口的

答:MDIO接口是用來配置外部的PHY芯片的,不是用來傳輸數(shù)據(jù)的,也就不是做網(wǎng)絡(luò)協(xié)議使用的。當(dāng)您需要配置外部的PHY芯片時,可以使用MDIO接口,否則可以不用。

【問題7.23】請問千兆網(wǎng)工程里,輸入給MAC_IP核的ff_rx_rdy信號為什么直接置1?跟速率和帶寬有關(guān)嗎?

答:rdy表示下游模塊準備好指示信號,如果準備好了就為1,沒準備好就為0。 在本案例中,下游模塊是rx_mac_analy模塊,該模塊支持rtl8122_a_mac_ip模塊任意速度的數(shù)據(jù),

即無論怎么來,下游模塊都能接收并正確處理,所以在此處置為1(時刻準備好)就可以了

【問題7.24】請問,一個基礎(chǔ)問題,千兆網(wǎng)工程里多個模塊都調(diào)用了FIFO,在不同模塊里調(diào)用的fifo的例化名(比如:u_dfifo)能否重復(fù)?

答:可以試試操作,在不同模塊是可以重復(fù)的。

【問題7.25】這個是因為IP核沒有破解嗎?

答:這個錯誤就是高版本生成的工程在低版本中打開出現(xiàn)的編譯錯誤,用高版本的quartus打開即可(如18版本的)

【問題7.26】千兆網(wǎng)課程使用的是哪個PHY芯片?

答:本課程使用的是MP801芯片,使用提RTL8211芯片。但課程中,幾乎沒有涉及到PHY芯片的內(nèi)容,PHY芯片使用的是默認配置。對于其他PHY芯片,也是通用的。

【問題7.27】千兆網(wǎng)課程是ALTERA,是否與XILINX的通用?

答:本課程主要涉及到各個協(xié)議的RTL實現(xiàn),這部分代碼是通用的。但有一個MAC IP核,本課程的工程是使用ALTERA的,XILINX的亦有相同的IP,需要您移植。總的來說,MAC IP占整個課程的比重不大,大概是5%的內(nèi)容。

【問題7.28】您的UDP教程里面包不包含ARP和CRC328bit這兩個地方的講解?

答:有arp的講解,但crc就不包括。

【問題7.29】千兆網(wǎng)課程的源碼中有相應(yīng)的tb仿真代碼嘛?

答:沒有,但如果要驗證功能正確性可以上板驗證和仿真文件

【問題7.30】請問下載程序后,電腦檢測不到本地以太網(wǎng),把程序刪除又可以檢測?

答:可能程序里有復(fù)位管腳,把這些PHY芯片復(fù)位了。

【問題7.31】以太網(wǎng)通信中,抓包工具wireshark能抓到 但網(wǎng)絡(luò)調(diào)試助手收不到 是怎么回事?

答:可能性有如下幾種,請逐一排除。

1. IP地址不正確,請檢查IP地址,尤其注意目的IP和源IP的區(qū)別

2. 端口號不正確,請檢查端口號,尤其注意目的端口和源端口的區(qū)分。

3. 目的MAC地址不正確,可以嘗試發(fā)送廣播包文(非ARP包文)測試。

4. 包文過短,小于60字節(jié)。

【問題7.32】工程仿真的前導(dǎo)碼后為什么有兩個字節(jié)的0呢? 按理說應(yīng)該緊跟目的MAC地址 圖中e8 6a就是目的MAC開頭.

答:MAC IP核的有一個32bit對齊的功能,關(guān)于該功能意義,請看【問題7.3】。如果出現(xiàn)上圖中問題,有可能是MAC IP核中的32bit對齊功能設(shè)置有誤。

【問題7.33】千兆網(wǎng)項目中,是否包括TCP協(xié)議實現(xiàn)?

答:千兆網(wǎng)項目是使用的UDP協(xié)議,而非TCP協(xié)議。目前來說,TCP協(xié)議由于有握手機制、重發(fā)機制等功能,在邏輯上實現(xiàn)相當(dāng)困難,暫未看到商用的案例。

【問題7.34】高速采集后的數(shù)據(jù) 是存到內(nèi)存或者flash嗎 ?

答:激光項目:采集到數(shù)據(jù)后,內(nèi)部進行計算和處理,并將結(jié)果通過千兆網(wǎng)上傳到上位機。大數(shù)據(jù)采集項目:從光纖采集到數(shù)據(jù)后,保存到DDR3中,然后讀出送到PCIE上位機。

【問題7.35】請問插上千兆網(wǎng)模塊后,PING不通?

答:千兆網(wǎng)模塊是一個基于PHY層的模塊,不是完整的網(wǎng)卡,實現(xiàn)的是PHY層的協(xié)議,沒有實現(xiàn)MAC層、TCP/IP層協(xié)議。

因此,不可能PING通(因為PING功能是在TCP/IP層實現(xiàn)的)。要實現(xiàn)PING功能,需要編寫FPGA程序來實現(xiàn)。

【問題7.36】插上設(shè)備后,電腦識別成百兆網(wǎng)問題?

答:上電后,電腦與千兆網(wǎng)模塊之間會開展自協(xié)商對話,根據(jù)雙方的環(huán)境確定通信速率。如果希望工作在1G,而實質(zhì)協(xié)商成100M,則依次按如下檢查。

1. 檢查電腦網(wǎng)卡是否支持1G,具體請看網(wǎng)卡設(shè)置

2. 檢查網(wǎng)線是否支持1G,有類型的要求。

3. 換臺電腦試試

4. 以上都測試過后還不行,請找指導(dǎo)老師確認。

【問題7.37】請問千兆網(wǎng)的rx_ip_analy.v文件,getlen是獲取總長度,第二個圖片get_len_4byte是完全不懂,請老師給個提示?還有+5又是什么意思呢?

答:IP長度是20字節(jié),get_len_byte是實質(zhì)獲取到的數(shù)據(jù)長度(不包括IP頭),單位為字節(jié);get_len_4byte是實質(zhì)獲取到的長度(包括IP頭),單位為32bite。

【問題7.38】你好,這個rx_ip_analy部分的,我不太清楚到底是實際的采集長度小于等于輸入獲取的長度還是輸入獲取的長度小于等于實際采集的長度。

感覺上面說應(yīng)該cnt <get_len_4byte,下面又說act_len_byte < get_len是錯的。

答:get_len:從長度字段獲取到的長度;

get_len_4byte:從長度字段獲取到的長度,單位為4字節(jié);

act_len_byte:從數(shù)據(jù)字段中獲取到的長度;

所以,從數(shù)據(jù)中獲取到的長度,小于“字段指示的長度”,就是錯的。

【問題7.39】請教大家一個問題,以太網(wǎng)調(diào)試的時候,主機網(wǎng)卡不是realtek PCIE FE Family,主機接收不到fpga發(fā)送的報文怎么辦?

答:一般來說,只要發(fā)送端發(fā)送的包文符合網(wǎng)口傳輸協(xié)議,無論什么網(wǎng)卡都可以都到包文。可以檢查一下

①fpga發(fā)送的包文協(xié)議是否正確;

②檢查網(wǎng)口識別的速率是否與工程速率匹配;

③檢查網(wǎng)卡是否有問題

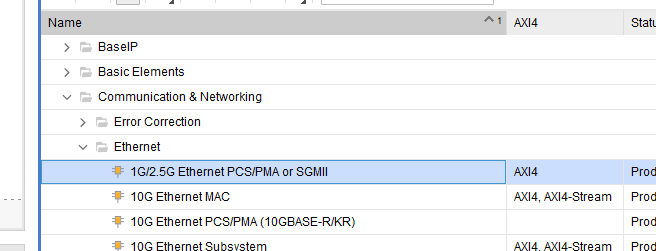

【問題7.40】千兆網(wǎng)工程使用sgmii接口,請問在vivado中用哪個ip核呀?

解答:GMII和RGMII接口使用的VIVADO?IP核為:tri_mode_ethernet_mac。而SGMII接口使用的IP核為:1G/2.5G Ethernet PCS/PMA OR SGMII。注意:SGMII模式,使用上面的這個IP核。注意,SGMII協(xié)議會與本課程中的MAC協(xié)議不同,要特別留意。

【問題7.41】問:千兆網(wǎng)課程的MAC是使用的官方IP核,還是自己RTL寫的?

答:本課程的UDP、IP、ARP等協(xié)議,是MDY的RTL代碼寫的。而MAC部分,使用的是官方IP核。在平時使用中,MDY也自己寫了簡化版的MAC層部分代碼,主要實現(xiàn)的是添加前導(dǎo)碼和校驗和。 這一部分沒有文字說明,也沒有教程,如果有疑問,請自行消化。下載鏈接如下:http://fpgabbs.com/forum.php?mod=viewthread&tid=4481&page=1&extra=#pid5534

【問題7.42】問題:以太網(wǎng)約束中,建立時間的時序報告如圖一,請問下為什么上面是4ns,下面又是加8ns呢? 保持時間分析如圖二,為什么這兩個都加4?

圖一

圖二

答:

1. 這項目是RGMII模式,時鐘為125M,上升沿和下降沿均采樣,相當(dāng)于時鐘周期是4ns。

2. 建議時間和保持時間都是從4ns開始計算,可能是約束時鐘時指定的,指定從4,可以看時鐘約束。(有些是從0開始)

3. 建立時間分析時,目的時鐘路徑要加上時鐘周期(4ns),保持時間分析時,目的時鐘路徑不需要加上時鐘周期。 原因請看時序約束問題匯總貼8.16 (http://old.mdy-edu.com/wentijieda/20210410/1294.html)。

【問題7.43】請問一下,IP校驗和,校驗和字段不加,這部分應(yīng)該是5吧,16*5。

解答: 如圖所示,ip_head[16*5-1 -:16]對應(yīng)的是IP校驗和的值,但此時還未計算出IP校驗和的值,所以ip_sum=0,因此可以省略對ip_head[16*5-1 -:16]的求和計算。

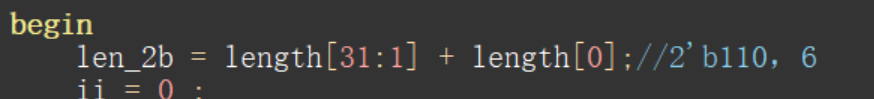

【問題7.44】想請問一下,以太網(wǎng)tx_pack模塊的測試文件,這條語句是什么作用呀?

解答:用于計算長度的有多少個2字節(jié)長度的數(shù)據(jù)。length表示長度有多少字節(jié),而len_2b表示長度有多少個2字節(jié)。信號length不取最低位,相當(dāng)于數(shù)據(jù)除以2。

【問題7.45】問:當(dāng)把板子和電腦的網(wǎng)線相連后,電腦那里顯示“未識別網(wǎng)絡(luò)”,如何解決“未識別網(wǎng)絡(luò)”問題?

答:“未識別網(wǎng)絡(luò)”這是正常現(xiàn)象。當(dāng)把FPGA板子和電腦相連后,無論FPGA有沒有程序,此時雙方通信均是“MAC層”的協(xié)議。該層協(xié)議只識別出速率,即1G還是100M速率。

而“未識別網(wǎng)絡(luò)”是指TCP/IP層的協(xié)議,需要TCP/IP層的完整協(xié)議支持,這是FPGA板子沒有的,也難以實現(xiàn)的功能,所以肯定是處于“未識別網(wǎng)絡(luò)”狀態(tài)。在真正應(yīng)用中,F(xiàn)PGA板子和電腦只是點對點通信,不需要組網(wǎng)。

【問題7.46】問:如果我想將GMII口換成RGMII口的話,是只需要將位寬以及MAC重新配置一下就可以了嗎?由于RGMII口是雙邊沿采樣,所以不確定需不需要加額外的操作。

我看網(wǎng)上用vivado的時候還需要用原語將phy給的rxclk處理一下才行。

答:將GMII口換成RGMII口的話,除了需要將位寬以及MAC重新配置一下,還需要更換一下硬件電路部分電阻。

【問題7.47】問:就是這個選項卡里面,勾選local loopback的時候,這個回環(huán)是MAC側(cè)回環(huán)還是phy側(cè)的回環(huán)呀

答:這個回環(huán)是MAC側(cè)回環(huán)。

【問題7.48】問:千兆網(wǎng)工程里有一個用戶時鐘:100M。這個100M時鐘是否可以用125M代替。

答:用戶時鐘只要大于75M即可。在提供的參考工程文檔里,有這個說明,可以看文檔。

【問題7.49】問:為什么是干什么用的?是不是IP頭?

答:偽首部僅是參與校驗和計算而使用的,不會放到包文中進行傳輸。

【問題7.50】問:如下圖,UDP包文協(xié)議中,各部分的位置在哪?

答:按照一個包文的先后順序,其包文字段分別是: 前導(dǎo)碼+MAC頭+IP頭+UDP頭(不包括偽首部)+UDP數(shù)據(jù)+校驗碼。

【問題7.51】問:接收方向做CRC校驗,是如何確認結(jié)果的正確性的?

答:CRC接收校驗有兩種方式。 第一種,接收過來的數(shù)據(jù)做CRC校驗,結(jié)果與接收過來的CRC校驗值比較,相同則接受正確,第二種,數(shù)據(jù)和接受過來的CRC結(jié)果一起做CRC校驗,結(jié)果應(yīng)該為“固定數(shù)”。注意,這里是固定一個數(shù),不一定是0,因為CRC算法里,還存在輸出結(jié)果反轉(zhuǎn)和異或等操作,會導(dǎo)致結(jié)果不一定為0。

【問題7.52】問:接收方向做CRC校驗,將數(shù)據(jù)和CRC位一起計算,結(jié)果一定是0嗎?

答:數(shù)據(jù)和接受過來的CRC結(jié)果一起做CRC校驗,結(jié)果應(yīng)該為“固定數(shù)”。注意,這里是固定一個數(shù),不一定是0,因為CRC算法里,還存在輸出結(jié)果反轉(zhuǎn)和異或等操作,會導(dǎo)致結(jié)果不一定為0。

【問題7.53】問:在千兆網(wǎng)工程中,很多模塊都有使用到了rdy信號,該信號的產(chǎn)生有些是跟FIFO的存儲數(shù)據(jù)個數(shù)關(guān)聯(lián)。如FIFO深度為4096,當(dāng)存儲數(shù)據(jù)大于4086時,rdy為0;小于4086時,rdy為1。為什么這樣設(shè)計?

答:rdy是本模塊準備好信號,為1時表示可以接收數(shù)據(jù),并且保證能夠正確處理。為0時,要求上游模塊不能發(fā)送。 當(dāng)FIFO滿了的話,進來的數(shù)據(jù)無法保存,就會丟失。所以滿了當(dāng)然rdy為0。為了讓上游模塊有一定的緩沖時間,將提示的水線設(shè)置小一些,例如4096的,就設(shè)為4086,這樣上游模塊可以晚幾個時鐘響應(yīng)也是可以的。 至于是4086,還是4090,根據(jù)項目情況自己設(shè)置。

【問題7.54】問:千兆以太網(wǎng)的macIP核部分的完整視頻有沒有?我看這個IP核說是也需要配置,還有ctc校驗,這些都是自動完成的嗎?

答:沒有,這部分不是直接使用就可以了,我們工程里有一個配置表代碼 直接可以用的,ctc是自動完成的 不需要參與

【問題7.55】問:請問老師這部分講解有嗎,找不到?

答:沒有講解,直接使用

【問題7.56】問:麻煩問下千兆以太網(wǎng)接收mac地址是0是怎么回事呢?

答:廣播包應(yīng)該是這么顯示的

【問題7.57】問:這個代碼里的注釋要怎么打開才看得到呢?

答:注釋變成亂碼:http://fpgabbs.com/forum.php?mod=viewthread&tid=813&highlight=%C2%D2%C2%EB

【問題7.58】千兆網(wǎng)課程提供工程源代碼嗎? 在課程網(wǎng)盤沒有找到,是哪個文件?

答:

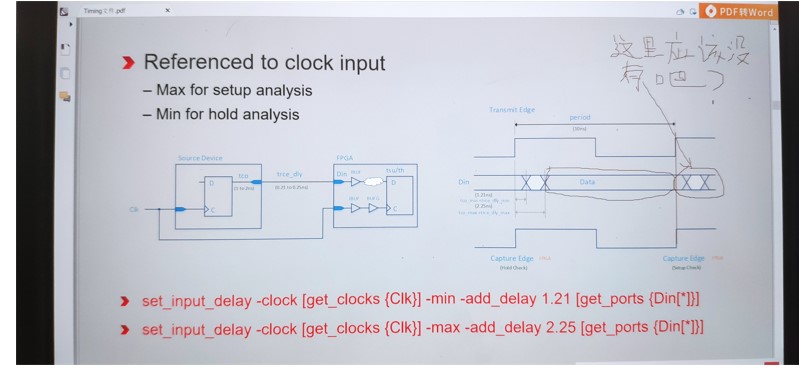

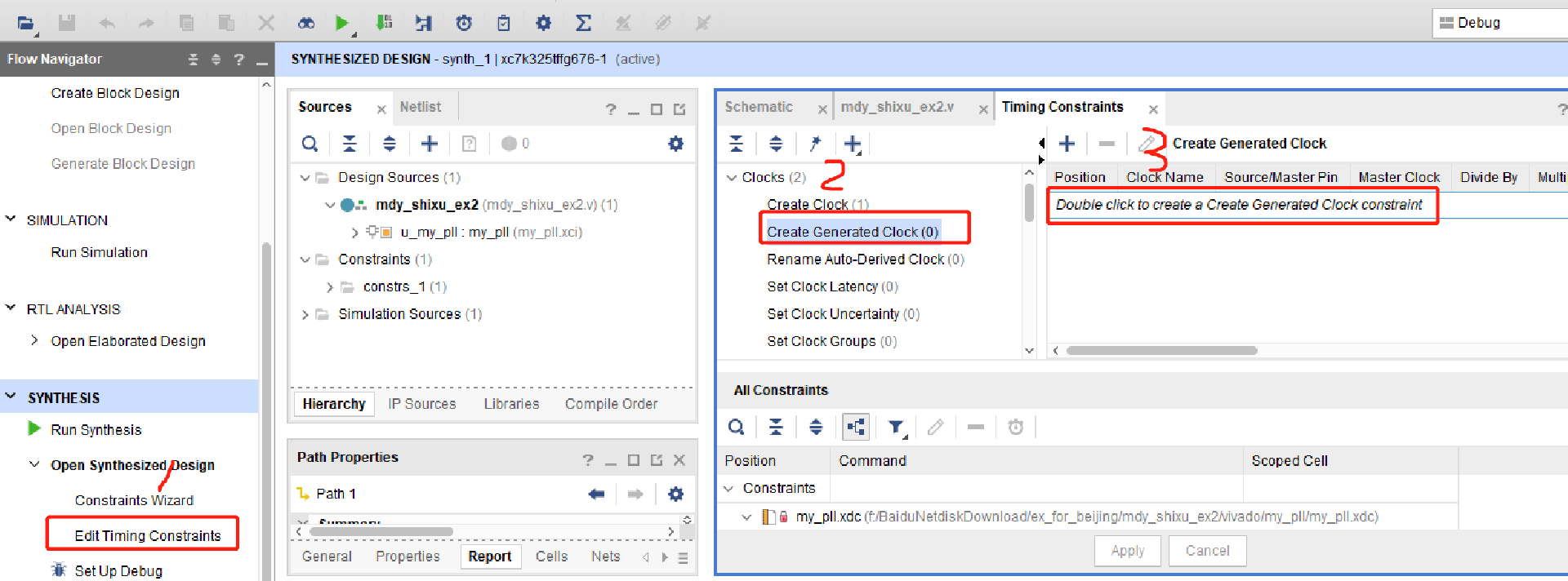

八、時序約束專題課

【問題8.1】 VIVADO的時鐘約束向?qū)Вo法找到時鐘,如下圖所示,位置1中應(yīng)該要識別出時鐘。

答:請注意,位置1的地方是列出的是“沒有被約束的時鐘”,如果該時鐘已經(jīng)被約束了,就不會在這里列出來了。注意上圖中3的位置,該列說明了有2條時鐘約束。可以點擊這里看看,是不是已經(jīng)對時鐘進行約束了。為什么會有時鐘被約束了呢?因為該工程已經(jīng)有約束文件。

【問題8.2】VIVADO/QUARTUS練習(xí)中,rst_n是否需要約束?

答:一個完整的約束,其基本要求是:所有的路徑都覆蓋,包括所有的輸入管腳和輸出管腳。所以,rst_n需要約束。注意的是,該信號是輸入信號,但沒有隨路時鐘進來。所以該信號可以認為是無時鐘的情形,按照課程理論,應(yīng)該定義一個虛擬時鐘。定義了虛擬時鐘后,再重新使用約束向?qū)Вs束rst_n。

【問題8.3】在VIVADO中,如何設(shè)置虛擬時鐘?

答:虛擬時鐘不能在時序約束向?qū)е刑砑樱枰谙旅娲翱谔砑?/span>

在Edit Timing Constraints中點擊,然后在creat clock窗口中,雙擊“Double click to create a Create Clock Constrtaint”。在彈出的窗口中

Clock name為該時鐘命一個名字,Source objects是不需要填的,因為是虛擬時鐘,就是沒對象了。

【問題8.4】時序約束出現(xiàn)時序違例(Slack為負數(shù)),如何處理?

答:首先指出一個誤區(qū):當(dāng)約束出現(xiàn)錯誤時,想當(dāng)然地認為是“時序約束做得不對”,所以應(yīng)該怎么去改“時序約束”,從而讓這些錯誤消失,這是一個錯誤的觀念。時序約束的作用:在于檢查“設(shè)計是否滿足時序要求”,它是用來審視自己設(shè)計的,很多情況是,要改設(shè)計代碼來滿足時序要求。當(dāng)時序約束提示有錯誤時,應(yīng)該閱讀“時序報告”,從報告中分析時序路徑(數(shù)據(jù)到達時間、時鐘到達時間和數(shù)據(jù)要求時間等),根據(jù)報告分析錯誤的原因,并根據(jù)原因來實行不同的方法。

以建立時間違例,說明具體方法如下

1. 時序報告中,找到提示錯誤的路徑,即目的寄存器,以及源寄存器。注意,這是兩個寄存器的點。

2. 首先判斷,源寄存器的時鐘,與目的寄存器的時鐘,是否相同。如果不同,可以認為是異步時序,見步驟3;如果是相同,則看步驟4。

3. 如果是異步電路,那么處理方法如下:

A. 確認做了異步處理。對于數(shù)據(jù),則是通過異步FIFO來做異步處理;如果是控制信號,則要經(jīng)過打兩拍來處理。

B. 確認做了異步處理后,仍然會報“時序違例”的。這個時候,可以該路徑設(shè)置成set false path,不用再檢查。

4. 同步電路下,具體處理如下:

A. 查看兩個寄存器點之間,經(jīng)過了多少加法器、乘法器、除法器等。

B. 對于除法器,要特別留意,一般是1個時鐘計算不完的。那么可以 a.想辦法不用除法;b. 通過使能信號控制獲取除法器結(jié)果的時間。

C. 對于乘法器和加法器,或者其他組合電路較多的。想辦法分隔成流水線來實現(xiàn)。可以參考MDY 流水線的內(nèi)容。

5. 如果是IP核的違例,檢查是否時鐘不滿足IP核的要求。如果沒問題,就不用管。

6. 如果是ILA等在線調(diào)試工具路線的違例,則一般不用處理。

7. 如果是線延時太長的,可以嘗試打一拍處理。即A->B的線太長,可以打一拍,變成A->C->B,這樣線延時就小了。

【問題8.5】VIVADO中,如何查詢未約束的時鐘、未約束的輸入延時和輸出延時等?

答:如下圖,在VIVADO的時序約束界面中,在下面欄目可顯示未約束的地方。

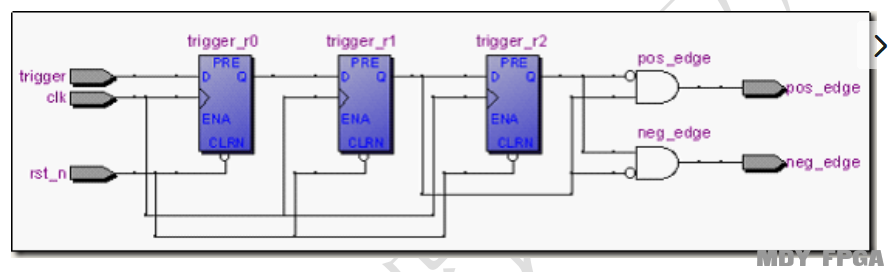

【問題8.6】如下圖所示,跨時鐘域打兩拍的方法,其實只是一個信號的傳遞,當(dāng)?shù)谝粋€信號出現(xiàn)不穩(wěn)之后或者錯誤之后,后面就會把這個錯誤的信號繼續(xù)傳遞下去,并沒有起到糾錯的作用

答:上圖中打兩拍的方法,其本質(zhì)不是為了“糾錯”,它的作用是為了防止“亞穩(wěn)態(tài)”。防止亞穩(wěn)態(tài)的本質(zhì):防止中間狀態(tài)過長。之所以采用兩級觸發(fā)器的方法,是因為D觸發(fā)器出現(xiàn)亞穩(wěn)態(tài)的可能性非常小,而兩級D觸發(fā)器出現(xiàn)亞穩(wěn)態(tài)的概率就更小了。

【問題8.7】既然打兩拍的方法不能糾錯,那“打兩拍”還有什么意義?

答:錯誤有很多種,有些錯誤是1次性錯誤,而有些是系統(tǒng)性錯誤。傳輸過程中,如果發(fā)了0,如果全部接收模塊都認為是1,這并不是問題,這是可以預(yù)防和可控的(例如檢測多幾次就行了)。

但是亞穩(wěn)態(tài)的時候,如果發(fā)了0,但部分接收認為認為是1,而另一部分模塊認為是0,至于哪些模塊認為是1哪些是0,這是隨機的,不可預(yù)知的,這就是災(zāi)難。

更詳細的內(nèi)容,建議參考:FPGA知識大串講 http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=581

【問題8.8】模塊A的時鐘clka為100MHz,模塊B的時鐘clkb為300MHz。現(xiàn)在模塊A要把32bit的數(shù)據(jù)送給模塊B。模塊A要如何發(fā)送,模塊B要如何接收呢?

答:

方法1:采用異步FIFO的方法。

方法2:采用指令信號的方法傳輸,模塊A產(chǎn)生vld信號給模塊B,模塊B對vld進行同步化處理(打兩拍)后,檢測同步化信號的上升沿。

需要注意的,VLD的信號是讓模塊B周期的三倍或以上。由于clka是100M,產(chǎn)生的vld是10ns,而clkb是300M,周期是3.33ns。所以模塊A只要產(chǎn)生1個時鐘的vld給模塊B即可。

【問題8.9】模塊A的時鐘clka為300MHz,模塊B的時鐘clkb為100MHz。現(xiàn)在模塊A要把32bit的數(shù)據(jù)送給模塊B。模塊A要如何發(fā)送,模塊B要如何接收呢?

答:

方法1:采用異步FIFO的方法。

方法2:采用指令信號的方法傳輸,模塊A產(chǎn)生vld信號給模塊B,模塊B對vld進行同步化處理(打兩拍)后,檢測同步化信號的上升沿。需要注意的,VLD的信號是讓模塊B周期的三倍或以上。

由于clka是300M,產(chǎn)生的vld是3.33ns,而clkb是100M,周期是10ns。所以模塊A要產(chǎn)生10個時鐘的vld給模塊B。

【問題8.10】一塊電路板上,有兩個芯片,芯片A的時鐘clka為100MHz,芯片B的時鐘clkb為100MHz。現(xiàn)在芯片A要把32bit的數(shù)據(jù)送給芯片B。模塊A要如何發(fā)送,模塊B要如何接收呢?

答:

方法1:采用異步FIFO的方法。

方法2:采用指令信號的方法傳輸,模塊A產(chǎn)生vld信號給模塊B,模塊B對vld進行同步化處理(打兩拍)后,檢測同步化信號的上升沿。需要注意的,VLD的信號是讓模塊B周期的三倍或以上。

雖然clka和clkb都是100M,但他們不是同一個晶振產(chǎn)生的,因此都是異步時鐘。為了滿足以上要求,所以模塊A要產(chǎn)生3個時鐘的vld給模塊B。

【問題8.11】A, B時鐘都是50M,但是他們不相關(guān),為了防止編譯器把他們默認為同一個時鐘,是不是要用一個異步時鐘組約束,來告訴編譯器他們是不同的兩個時鐘?

答:一般分別產(chǎn)生A和B的時鐘約束即可。

【問題12】 建立時間可以是負值嗎?

答:建立時間當(dāng)然可以是負數(shù)了。負數(shù)表示,可以在時鐘上升沿后數(shù)據(jù)才變化。(建立時間是器件的屬性,至于怎么器件怎么做到的,那就要問器件工程師了)

【問題13】 程序原本時序可以通過,加上singalTap節(jié)點之后時序不通過是什么原因

答:增加signaltap ILA等在線調(diào)試工具時,需要使用到內(nèi)部的資源,例如RAM、選擇器、寄存器等,增加后再去綜合和布局布線。由于改變了資源,因此肯定對時序是有影響的,有可能改善了也有可能惡化了。如果時序有問題,分析路徑,如果是在線調(diào)試工具路徑,評估是否會有風(fēng)險,沒風(fēng)險就算了

【問題8.14】時序約束什么時候要做?

答:

1.在需要的時鐘頻率下,如果邏輯功能不穩(wěn)定,那么就需要時序約束。

2.一般時鐘大于100M的時候,我們就要做一下時序約束。

【問題8.15】時序約束建立時間和保持時間的生活案例。

答:可以想象,有一個人從家里出發(fā)去機場,搭乘13點的飛機。

1. 13點起飛,起飛前15分鐘要到機場,這個15分鐘,就類似于建立時間要求。

2. 機場每小時有要飛一趟飛機,每個小時表示的是時鐘周期。

3. 飛機起飛后,機場要保持10分鐘,之后才能來下一批乘客,這個10分鐘就是保持時間。

4. 這個人出發(fā)去搭13點的飛機,因此他要在12點45分之前到機場,并且是12點10分之后到機場。既不能早到,也不能晚到機場。

5. 如果這個人12點45分之后才到機場,那就搭不上本趟飛機,即違反了建立時間要求。(建立時間影響的是自己坐飛機)

6. 如果這個人12點10分前就到了機場,那就會因此上一趟飛機的起飛,即違反了保持時間要求。(保持時間不滿足,影響的是上一批乘客坐飛機)

7. 這個人是計劃去機場,因此他要估算幾點能到機場。首先他會算所有情況下的最大延遲,如剛到路口紅燈就來了、走路最慢等,在這種最慢的情況下,如果能在12點45分前到,說明建立時間沒問題。然后,他會算所有情況下的最小延遲,如剛到路口綠燈,走路最快,在這種最快的情況下,如果能在12點10分后才,那說明保持時間沒問題。

【問題8.16】為什么建立時間分析的時鐘到達時間要加一個時鐘周期而保持時間分析則不用呢?

答: 因為建立時間是源寄存器發(fā)出數(shù)據(jù),目的寄存器采集,也就是上一個時鐘發(fā)出來,本時鐘采集。這里有一個時鐘周期的因素,所以要加1個時鐘周期。而保持時間分析,則是“本個時鐘”發(fā)出數(shù)據(jù)后,如果延時太小,會影響“本個時鐘”對上一個數(shù)據(jù)的采集,因為不需要加1個時鐘周期。另外,要注意一點,保持時間是跟時鐘周期無關(guān)的。

【問題8.17】一個外部的信號,經(jīng)過狀態(tài)機的“組合邏輯”,這也要做同步處理嗎?

答:需要做同步處理的。首先明白一點,F(xiàn)PGA里的時序邏輯=組合邏輯 + D觸發(fā)器。組合邏輯的最終結(jié)果,還是要發(fā)D觸發(fā)器的。所以還要做同步化處理的。

【問題8.18】請教下,做時序約束,做到這步時,這些都要勾選上嗎?

答:當(dāng)然不是,要逐個分析確認,沒有一選就全選上的道理。

【問題8.19】下面的生成時鐘約束,是否一定要勾選?

答:這應(yīng)該看生成時鐘那一節(jié)視頻,里面重點強調(diào)了“什么叫時鐘”? 上面的圖里,您應(yīng)該要搞清楚,它被識別出時鐘了,正不正常?如果是正常,那您肯定是要添加約束,定義頻率吧。如果它不應(yīng)該識別出時鐘了,

那您應(yīng)該檢查您的代碼,看是不是代碼不規(guī)范引起,或者有沒有潛在的問題。注意一下:約束不是目的,約束是為了查看報告,看設(shè)計有沒有問題的。

【問題8.20】系統(tǒng)同步只可能是單沿采集?沒法像DDR那樣雙沿采集?

答:系統(tǒng)同步也是可以是雙沿采集的,但比較少。課程里,只是介紹了部分情形。如果想看所有情形有哪些,可以打開VIVADO的時序約束向?qū)В梢栽O(shè)置INPUT DELAY窗口查看。

【問題8.21】QUARTUS生成SDC時,默認出現(xiàn)的那條時鐘約束是正常的么?我自己刪掉就行了?

答:默認生成的當(dāng)然是不正常。

【問題8.22】老師問一下,我畫的后邊那個部分,我認為應(yīng)該沒有數(shù)據(jù)吧?

答:不是 這個不是有沒有數(shù)據(jù)的概念 而是數(shù)據(jù)是否穩(wěn)定的概念。

【問題8.23】請問下有沒有針對SDC時序約束語法的講解嗎?

答:時序約束里,只講解了用到的部分。如果想看更多部分,我估計你要看這個語法的權(quán)威資料了。

【問題8.24】老師您好,我在學(xué)習(xí)時序約束視頻,看到第一個視頻這塊“流水線設(shè)計思路:乘法器可以分成加法器,然后加法器還可以分成什么,一直聽不清”

答:最后可以分成與門這些最簡單的門電路。

【問題8.25】老師請問紅色的是不是不滿足時序要求?

答:不是的,setup和hold時間形成一個時間窗,只要在這個時間窗里信號穩(wěn)定就餓可以了 在使用時序分析工具的時候,字體為紅色時間提示是不滿足時序要求

【問題8.26】什么樣的信號會被工具判斷為時鐘?

答:一個信號被VIVADO QUARTUS判斷為時鐘,不是看名稱里是否帶有“clk”等字母。而是主要看其是否用于“時鐘”的行為中,主要有如下幾種情況。

1. 被關(guān)聯(lián)到always敏感列表里的時鐘信號。說明會被連到觸發(fā)器的時鐘端,所以會被認為為時鐘。

2. 被連到PLL和MMCM等時鐘管理器的輸入端,這會被認為是時鐘。

3. 被連到鎖存器的條件端,例如一個沒有補全的組合邏輯代碼,其條件就會被認為時鐘。

【問題8.27】用ila抓取信號分析,發(fā)現(xiàn)異常,而時序約束報告正常,因此可以認為時序報告正常,而時序會有問題?

答:

1.在線邏輯分析儀是用于判斷邏輯是否出現(xiàn)問題,可以認為是檢查時鐘節(jié)拍下的邏輯判斷。而時序約束是解決D觸發(fā)器的建立時間和保持時間問題,是一個時鐘內(nèi)的時序問題。所以,不能用ila來推導(dǎo)時序約束,這是不同層次的問題。

2.官方可以保證,用戶代碼和時序約束的生成結(jié)果是正確,即在輸入的代碼和約束,給出來的報告一定是正確的。但時序約束對不對,這是客戶保證的。

3.出現(xiàn)結(jié)果不對,可能性很多,不一定是時序問題,要注意“充分必要條件”。

【問題8.28】同樣的工程不做任何改動,有時編譯后下板驗證正確,有時編譯后下板驗證不正確,是不是時序問題呢?

答:有可能是,但又不一定是。這是時序不滿足的一種現(xiàn)象。但反過來,沒有說,出現(xiàn)這種現(xiàn)象,就一定是時序問題。

【問題8.29】設(shè)置時鐘約束時,假如有虛擬時鐘的情況,虛擬時鐘是必須要設(shè)置的嗎?

答:

1.原則上所有接口有應(yīng)有約束。

2.設(shè)置虛擬時鐘,可以方便將對應(yīng)信號歸到該虛擬時鐘好,這樣方便做分析,例如看有沒有跨時鐘域等。

3.是不是一定要做,取決于項目老大要求,不做不一定有問題。

【問題8.30】一個always模塊下,if 、else if,,,else ,寫的太多了 ,是不是會容易造成時序問題呢?這種說法對嗎?

答:這里有一個定義要搞清楚的,什么叫“多”?

1. 是3個就多,還是10個?每個人標(biāo)準不同。

2. 即使是同一個人,使用不同的器件,這個“多”也是不同的。有些高級的器件,10個IF也不多,有些低端器件,3個也多。

3. 即使同一個人,同一個器件,但if里的判斷條件也有講究。如果判斷條件里一個除法器,那1個if也多,如果只是判斷0和1,那么10個也算少。

4. 最具可操作性的做法,給定時鐘約束,看時序報告。報告沒問題,那就是沒問題;否則會有時序違例的錯誤。

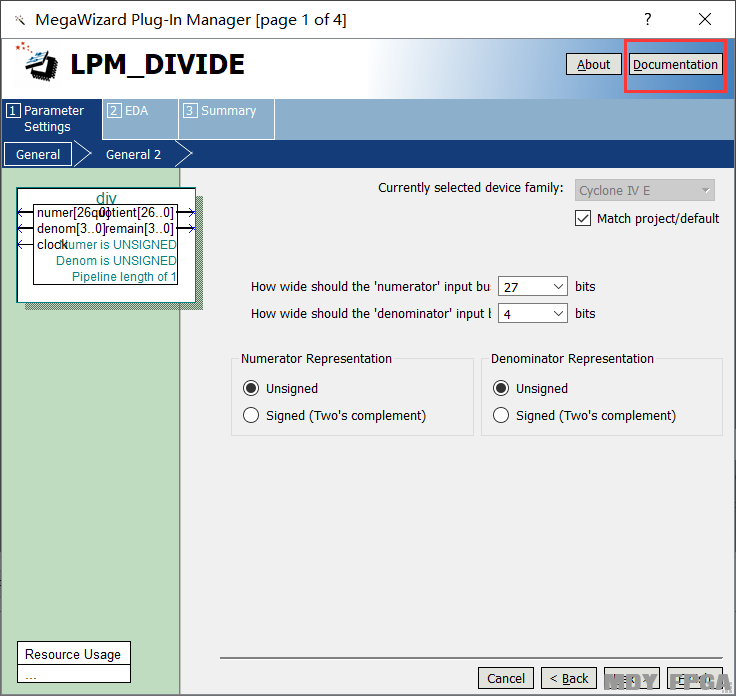

【問題8.31】output latency一般設(shè)置成多少呢?pipeline 有啥用?

答:由于除法器占用資源較大,難以在一個時鐘周期內(nèi)計算完畢,需要多個時鐘才計算完,這個pipeline就是設(shè)置多少個時鐘周期的。

如果您不清楚要多少個,設(shè)置填一個較大的數(shù),然后看時序報告是否正確。如果正確,就沒問題。

【問題8.32】請問:MDY的案例中,為什么串口需要對din進行同步化,而SCCB就不需要對sio_din進行同步化?sio_din也是外部器件進來的嗎?

答: 是否要對信號進行同步化,最核心的理解是“該信號是否能夠保證滿足建立時間和保持時間要求”,也就是“該信號的變化和時鐘存在確定性相位關(guān)系”。

以串口為例,串口的輸入信號與FPGA時鐘是沒有任何聯(lián)系的,該輸入信號可以在任意時刻變化,也就有可能剛好在時鐘上升沿變化,從而不滿足建立時間要求,

因此要做同步化處理。而SCCB案例中,由FPGA時鐘里產(chǎn)生了sio_dout、SCK等信號,而sio_din在sck作用下變化,所以sio_din與FPGA時鐘是有一定關(guān)系的。

可以認真看時序圖,在FPGA對sio_din有采樣時刻,時序已經(jīng)要求sio_din要穩(wěn)定不變的,所以可以不用做同化處理。

【問題8.33】請問工程中使用了PLL,在做時序約束時,generate clocks窗口顯示沒有PLL產(chǎn)生的時鐘,如下圖,為什么?

答:PLL、MMCM等產(chǎn)生的時鐘,默認是由工具自動推導(dǎo)約束的,不用用戶來約束。雖然用戶沒有約束,事實上是做了分析的。例如下圖中,

可以看到c0_my_pll這個時鐘。其中,c0_my_pll是工具自動命名的。

用戶也可以自己約束PLL/MMCM產(chǎn)生的時鐘,方法如下圖。

按照方面方法,約束好,重新分析就可以了。

【問題8.34】問:如果使用的IP核內(nèi)部代碼出現(xiàn)了時序約束違例,該如何解決?

答:IP核是由官方提供的代碼,一般用戶不能修改,如果該IP核出現(xiàn)違例,可以從以下方向入手:

1. 一般IP核是有指定的頻率范圍,可以從數(shù)據(jù)手冊找到,請看是否滿足了數(shù)據(jù)手冊要求。

2. 如果頻率正確,還會出現(xiàn)報錯,可以檢查時鐘和復(fù)位管腳有沒有正確使用,根據(jù)經(jīng)驗,這通常是引起問題的原因。

3. 嘗試修改編譯策略,重新綜合看看。

【問題8.35】問:請問時序約束只是針對FPGA輸入與輸出端進行約束,而不是針對FPGA內(nèi)部模塊之間或者模塊里面。這樣理解是否正確?

答:不是的,內(nèi)部肯定也跟約束有關(guān)。

【問題8.36】問:老師,想問下時序約束,DDR4的uiclk需要時鐘約束嗎?

答:需要的,設(shè)置好時鐘頻率,周期就可以了,就是需要create clock就好了

【問題8.37】問:關(guān)于input delay的抖動解釋。

答:需要理解的抖動,不是指一個波形的結(jié)果,是多個波形疊加的結(jié)果。假設(shè)說一個PWM波形,周期為10ns,理想情況下變高為2.5ns,變低在7.5ns。由于存在不確定延時情況,所以有時候變高在2.6ns,變低在7.6ns。有時候變高在2.4ns,變低在7.4ns。有時變高在2.3ns,變低在7.3ns。數(shù)個波形疊加,就看到了抖動的現(xiàn)象。

| 九、PCIE專題課 【問題9.1】 PCIE視頻教程是否有講簡單的pio數(shù)據(jù)交互? 【問題9.2】多少通道都可以嗎? 【問題9.3】為什么我得pcie板卡驅(qū)動識別為PCI standard RAM Controller而不是pci設(shè)備或者未知設(shè)備呢? 【問題9.4】請問課程可以在VIVADO平臺開發(fā)是嗎?

十、就業(yè)班項目-光纖項目 【問題10.1】光纖項目主要是培訓(xùn)內(nèi)容是哪些接口?

【問題10.4】光纖ip 核的輸入時鐘是156.25M hz,輸出時鐘是多少呢?

【問題10.10】老師您好,高速光纖通信項目通過光纖接口進來的數(shù)據(jù)量是多大的?DDR中需要存放多少數(shù)據(jù)呢?

【問題10.12】老師您好,高速光纖通信項目通過光纖接口進來的是什么數(shù)據(jù),出去的又是什么數(shù)據(jù)呢?

【問題10.15】問:使用同步碼(charisk)有沒有使用規(guī)則,或者有沒有注意事項,要注意什么?

【問題10.17】光纖項目里的學(xué)員筆記,是用什么工具畫的阿

【問題10.19】問:光纖項目中,GTX是使用的哪個IP核? 【問題10.20】問:整體流程用了k7多少資源?

十一、就業(yè)班項目-精密儀器項目(JESD204B) 【問題11.1】JESD204B專題課有交流群嗎? 【問題11.2】交流群會解答哪方面的內(nèi)容? 【問題11.3】FPGA的JESD204B參考文檔是PG066嗎?

答:要使用AD9144成功,可以依次檢查以下AD9144的幾個寄存器。 地址OX470:該寄存器用于表示LANE有沒有檢測到K28.5同步字。如果說FPGA管腳配置錯誤、時鐘有問題、LANE速率有問題(例如雙方配置的LANE速率不同,一端為2G,另一端為2.5G;或者信號質(zhì)量不高,傳輸有誤碼等),則讀到的值將不正確。 地址OX471:檢查是否所有的LANE都已經(jīng)同步。如果地址0X470正確,本寄存器不正確,則可能是速率、時鐘有問題。 地址OX472:檢查checksum,即校驗和是否正確。如果說FPGA和AD9144的參數(shù)不同,或者是傳遞有錯誤,則此寄存器值不正確。 地址OX473: 檢查ILAS。如果說此正確,基本上都正確了。

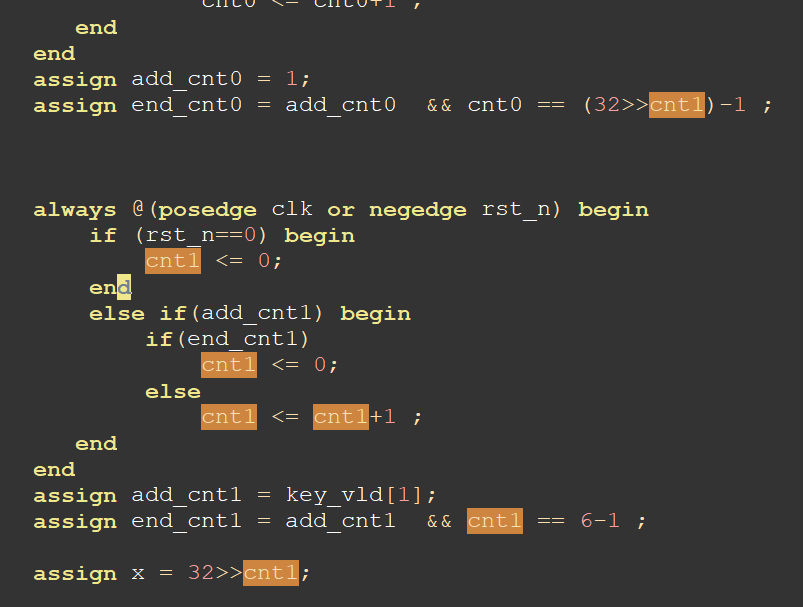

答: 本工程有一個功能,通過按下按鍵,可以改變信號的頻率。工程一共支持6種頻率,cnt1值為0~5,分別用來表示6種頻率。上面代碼中的cnt0控制頻率的,其是通過控制同一值重復(fù)的次數(shù)來達到控制頻率的目的,例如假設(shè)某信號值為01234為100M信號頻率,讓每個點重復(fù)一次,即0011223344,信號頻率就變?yōu)?0M。cnt0的值根據(jù)cnt1來改變,例如當(dāng)cnt1為0時,cnt0的值為0~31,當(dāng)cnt1為1時,cnt0的值為0~15,當(dāng)cnt2為2時,cnt0的值為0~7。

上圖中,依次是確定需求,即您希望的信號頻率、采樣率DAC個數(shù)分別是多少,然后據(jù)此確定需要多少條LANE;進而確定AD9144的配置;lane的,速率;sample時鐘等等。本課程有對應(yīng)的視頻講解,可以詳細理解。請理解視頻中介紹的思想,從而應(yīng)用到您自己的項目中。實用建議:建議您在我們提供的案例基礎(chǔ)上,每次改動一點點,看到正確效果后,再做下一下,最終完成最終的目標(biāo)。 【問題11.7】案例中,插值為2的意義?為什么要插值?

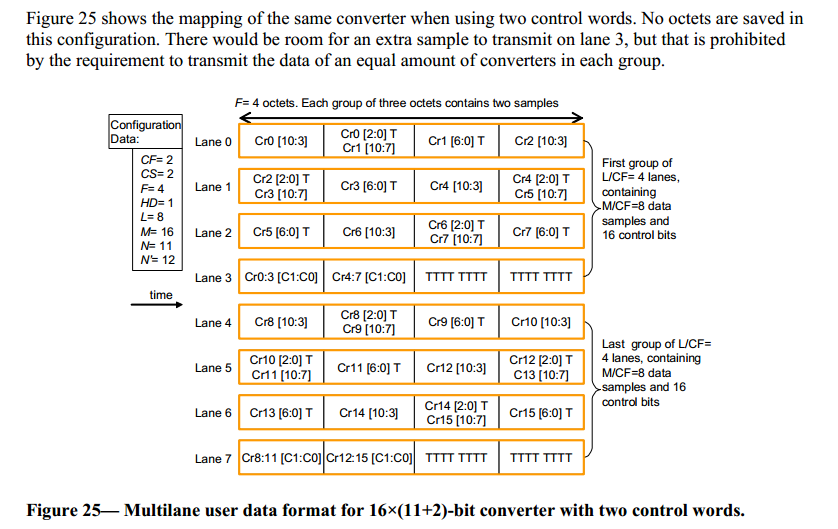

答:CS是指一個SAMPLE中的控制位比特數(shù),上面兩種情況,每個SAMPLE都加了2位的控制比特,即圖中的C1和C0。 注意,圖中的“Cr0:3[C1:C0]”,是指Cr0的[C1:C0]+Cr1的[C1:C0]+Cr2的[C1:C0]+Cr3的[C1:C0]。CF是指一個FRAME CLK中的控制字個數(shù),單位為字節(jié)。注意,這里的CF的限定條件是一個“FRAME CLK”。一個FRAME CLK,即上圖中的一列數(shù)據(jù)。 從第一個圖可以看出,第一列控制字是Cr0:3[C1:C0],共8比特,所以為CF=1。 從第二個圖可以看出,第一列控制字是Cr0:3[C1:C0]和Cr8:11[C1:C0],一列共有16比特,所以CF=2 【問題11.9】在講解需求時,下面的16是什么含義?

首先,明確概念,SERDIN0~7指的是AD9144芯片上定義的管腳,是物理的,可以去看管腳圖。LANE0~7,是指內(nèi)部表示的LANE編號。 估計是為了靈活性,LANE0~7不是與SDRDIN0~7不是一個一個對應(yīng)的,其對應(yīng)關(guān)系是可以配置的,上面幾個寄存器就是起這種作用。 例如,LANE0可以與SERDIN0對應(yīng),這個時候的0X308[2:0]=0,也可以和SERDIN4對應(yīng)起來,這個時候0X308[2:0]=4。 其次,理解了上面關(guān)系后。你可以根據(jù)實際情況來配置,例如,本案例中的AD9144子板,它的SERDIN0~3是沒有用的,只使用了SERDIN4~7,這是 固定死的。然后內(nèi)部的配置,您可以使用LANE4~7來對應(yīng)SERDIN4~7,也可以使用LANE0~3來對應(yīng)SERDIN4~7,這由您來決定,都是可以實現(xiàn)的。 最后,再強調(diào)一下工程思維:芯片提供了很多功能,您用也可以,不用也可以,您會怎么做?你就選擇最簡單的來做,甚至就是忽視它存在,也就是使用默認值。

【問題11.16】為什么v5版本是6.4Glane速率,而v7就是3.2Glane速率了,都是10~40M的正弦波啊?

【問題11.27】204b,通過lane傳輸?shù)臅r候,fpga不用單獨給DAC提供時鐘,而是通過CDR從lane數(shù)據(jù)線中恢復(fù)出時鐘,這樣理解對嗎?那還有output delay嗎?

|

【問題11.33】是否包含有高速AD/DA的項目?最高速率是多少?有多少路?

答:激光工程項目中,包含有高速ADC AD9684,速率是500M,目前是支持一路的實現(xiàn)。精密儀器項目中,包含有高速的DAC AD9144,目前實現(xiàn)的最高速率是1G,支持2路輸出。

【問題11.34】精密儀器項目中,AD9144的AD測量范圍,DA輸出的范圍,以及采樣率分別是多少?

答:AD9144是一款DAC芯片,所以沒有AD測量范圍。DA采樣率我們實現(xiàn)的是1G,實質(zhì)可達1.8G。DA輸出范圍以及更多信息,請參考以下數(shù)據(jù)手冊。

![]() AD9144-FMC-EBZ RevB Schematic.pdf (79.85 KB, 下載次數(shù): 0)

AD9144-FMC-EBZ RevB Schematic.pdf (79.85 KB, 下載次數(shù): 0) ![]() AD9144.pdf (2.79 MB, 下載次數(shù): 0)2020-11-4 10:55 上傳,點擊文件名下載附件

AD9144.pdf (2.79 MB, 下載次數(shù): 0)2020-11-4 10:55 上傳,點擊文件名下載附件

【問題11.35】JESD204B課程中,是那種并口高速adc用的那種協(xié)議么?

答:不是高速并行口,而是高速串行口,即SERDES接口來實現(xiàn),單根線的速率可達到10G。

【問題11.36】就業(yè)班企業(yè)項目里視頻拼接MIPI項目有用到IP核嗎?需要額外交IP核費用嗎?

答:MIPI項目是用的lattice芯片,lattice的此IP是免費的,學(xué)習(xí)此項目無需額外繳費。

【問題11.37】申請JESD的臨時License提示不符合出口規(guī)定,有沒有什么其它辦法?

答:換了個企業(yè)郵箱賬號就行了

【問題11.38】一,首先我得讀9156寄存器,二,我的讀9154{我自己的dac}三,用 dpg..現(xiàn)在dpg軟件駛不了,麻煩解答一下

答:我們提供的例程,已集成在工程里面的,全部代碼是FPGA代碼。

【問題11.39】請問9144用的是mose0,配置完后,CGS可以過,可以讀到寄存器470是FF,8個lane都收到了k28.5,但是寄存器023的bit1一直在01之間不停的跳動,代表FIFO的讀寫一直有錯誤,查看30c和30d也能看到錯誤標(biāo)記,此時發(fā)送sysref的話,ILAS也能過,但是470,471,472,473都在不停的跳動,sync標(biāo)記也是忽高忽低,此時鏈路不穩(wěn)定,給tx核送數(shù)據(jù),在頻譜儀上能看到9144的輸出,但是因為鏈路不穩(wěn)定,輸出會不停的閃爍,理論上講,鏈路穩(wěn)定的話,470.471.472.473都應(yīng)該回讀FF才對,我想請教一下,是什么導(dǎo)致了9144配置完后fifo的讀寫標(biāo)記一直報錯呢?也就是寄存器023的bit 1

答:如果是自己做的硬件板,則有可能是硬件的穩(wěn)定性問題。請檢查硬件電路。

【問題11.40】請教一個問題,204b時序不行。12.5g,312.5M的核時鐘。一個dac時序違例不嚴重能工作,另一個不行,怎么處理

答:解決時序違例,其思路是減少組合電路邏輯。如果確實無法減小,那就只能降低時鐘頻率了。您使用的315.5M是工作時鐘的話,那確實是太高了,建議可以將工作時鐘降為156.25M

【問題11.41】請問按鍵是有4位., 但代碼中只使用了0位和1位, 這按鍵有沒有順序要求, 先按哪個再按哪個? 然后這個這個按鍵信號作為使能信號, 是只持續(xù)一個時鐘, 還是需要一直為高?

答:先按啟動有效的按鍵,再按改變頻率的按鍵,具體請看使用說明。

【問題11.42】請問在給JESD204C IP核配置的時候,讀取0x020 RESET寄存器的值,讀到的值是0x081,說明這個IP一直處于復(fù)位狀態(tài),無法從復(fù)位狀態(tài)退出,可能是什么問題呢?

答:檢查一下所有的時鐘和復(fù)位信號,一般都是跟這些信號有關(guān)

【問題11.43】請問FPGA中的204B IP核,其配置是在哪里定義?

答:JESD204B的IP核配置,其地址在addr.coe文件中定義;其寄存器值在data.coe文件中定義。

【問題11.44】device clock是什么意思?

答:可以認為是AD9516給FPGA的一個多幀時鐘,用于同步多幀的,可以認為D個多幀就發(fā)一個上升沿,這樣就好同步了。具體有一個視頻,可以看JESD204B協(xié)議04_實踐_協(xié)議各個時鐘的關(guān)系。

【問題11.45】:課程提供的上位機軟件是直接和dac連接用于檢測dac里寄存器的值嗎?還是dac通過傳數(shù)據(jù)到fpga通過fpga連接呢?

答:

做法1:上位機將寄存器配置值寫到FPGA,F(xiàn)PGA再寫到DAC里。

做法2:FPGA內(nèi)部有配置表,上電后自動配置DAC的寄存器。 以上兩種方法都有。

【問題11.46】:如果是通過fpga連接的,是走的uart還是ethernet呢?

答:走的是網(wǎng)口。

【問題11.47】:vc707可不可以兼容我們的程序?

答:只要有HPC接口的,均支持

【問題11.48】:是不是地址8的ILA support設(shè)為1就代表在CGS之后開啟ILAS的功能?

答:該地址設(shè)為1,表示啟動ILA功能,設(shè)為0表示不啟用。

【問題11.49】:地址20的ILA multiframe是選擇ILAS一共發(fā)送幾組8位數(shù)據(jù)?我們設(shè)為3就代表發(fā)送4組8位數(shù)據(jù)?

答:這里不是以8位數(shù)據(jù)為音位,而是multiframe為單位。所以設(shè)為3,表示發(fā)送4個多幀數(shù)據(jù)。

【問題11.50】:地址2060和2072的ILA config data 3 和 6 功能似乎是Sets the values to be transmitted in the ILA sequence for all lanes. 這兩個寄存器是用于設(shè)置ILAS發(fā)送的數(shù)據(jù)嗎?

兩個寄存器都是0那發(fā)送的ILAS是全0,還是某個默認值?我看到網(wǎng)上有說是k28.0到k28.4順序發(fā)送的,但我看我的一個TI的dac好像默認是0x1C也就是K28.0

答:這里是設(shè)置需要的L、BID、LID和DID等參數(shù)。從字面上理解,發(fā)送方向就會把這些數(shù)據(jù)當(dāng)成ILA數(shù)據(jù)發(fā)給對端。按真實要求配置即可。設(shè)了什么值,就會打包成對應(yīng)數(shù)據(jù)發(fā)送給對端。至于如何打包,我這還沒有研究。

【問題11.51】:multiframe包含幾個frame?

答:這個每個工程不同,是可以靈活設(shè)計的參數(shù),并且是與時鐘頻率、其他參數(shù)相關(guān)聯(lián)的。

【問題11.52】:BID這些參數(shù)具體就要從DAC那邊找到對應(yīng)的然后兩邊匹配就可以了,是嗎?

答:BID DID 這些,兩邊匹配即可。

【問題11.53】麻煩問一下這個sin_data數(shù)據(jù)是怎么來的?自己造的數(shù)據(jù)嗎?

答:sin_data是正弦波的數(shù)據(jù),該正弦波數(shù)據(jù)用matlab產(chǎn)生,模塊這里是轉(zhuǎn)化成verilog語言后的。

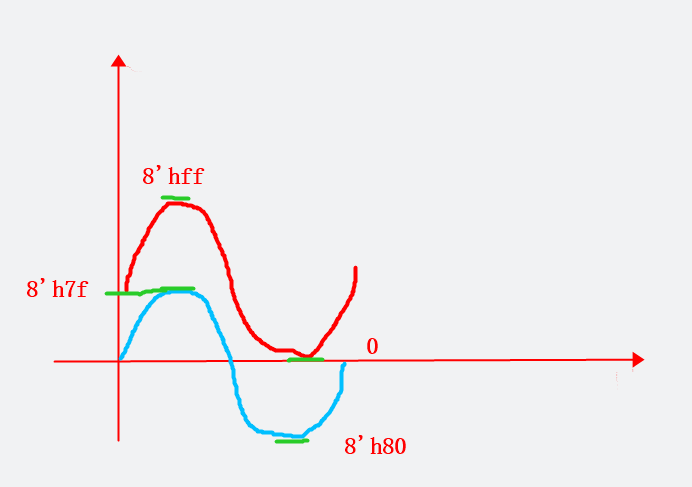

【問題11.54】減得那個8'h80是什么意思呢?為什么要減那個8'h80呢?

答:如圖紅色波形所示,該正弦波數(shù)據(jù)用8bit位寬表示,0~8'hff是它的幅度值范圍,中間的幅度值為8'h7f。 而在工程需求里,接口要求輸出的正弦波數(shù)據(jù)為補碼形式,那么正弦波的補碼波形如圖藍色波形所示, 補碼表示的最高點數(shù)值為8'h7f,最低點數(shù)值8'h80。對于數(shù)值8'h80+1=8'h01,8'h80-1=8'h7f,那么將正弦波數(shù)據(jù)sin_data-8'h80得到的就是如圖藍色的波形數(shù)據(jù),也是一個補碼的數(shù)據(jù)。

【問題11.55】問題:請問jesd204 phy能選擇具體某一個quad嗎?具體如何選?

答:JESD204 PHY是可以選擇QUAD的,在IP核界面里可以選擇使用哪個,具體可以教程里的視頻

【問題11.56】JESD204B課程是ADC采樣,還是DAC采樣?(模數(shù)轉(zhuǎn)換是ADC,數(shù)模轉(zhuǎn)換是DAC)

答:是DAC采樣

【問題11.57】Jesd204B那個項目里的以太網(wǎng)通信是不是沒有調(diào)用MAC ip核,自己寫的

答:是的。該代碼沒有調(diào)用IP核,純RTL實現(xiàn),模塊名為gmii

【問題11.58】fmcAD9144模塊從jp2送入AD9516的時鐘信號需要多大幅值的?1.8V夠嗎?

答:一般JP2的時鐘幅值為1.5V。1.8V也是可以的

【問題11.59】問:我JESD204B ADC接受的數(shù)據(jù)全是0咋回事?

答:

1.確認接收到了數(shù)據(jù)?

2.基于1后,再確認是 0

【問題11.60】問:這個sysref信號必須由外部提供嗎?我們板子沒有這個信號,能不能用device clk這個信號分頻得到?

1.時鐘要穩(wěn)定;

2. 兩邊都是完全同頻同步的時鐘

【問題11.61】問:老師我想問一下jesd項目里的9516和9144的配置視頻里講的是通過ACE工具和上位機軟件配置的,那vivado程序中又有配置模塊,這是怎么回事?

答:前期工程是由上位機配置的,后面提供的工程 由內(nèi)部模塊配置的

溫馨提示:明德?lián)P2023推出了全新課程——邏輯設(shè)計基本功修煉課,降低學(xué)習(xí)FPGA門檻的同時,增加了學(xué)習(xí)的趣味性,并組織了考試贏積分活動

http://m.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯(lián)系易老師:13112063618(微信同步)

明德?lián)P除了培訓(xùn)學(xué)習(xí)還有項目承接業(yè)務(wù),擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(IMX472 IMX492)

3. PCIE采集系統(tǒng)

4. 圖像項目

5. 高速多通道ADDA系統(tǒng)

6. 基于FPGA板卡研發(fā)

7. 多通道高靈敏電荷放大器

8. 射頻前端