1、 項目背景

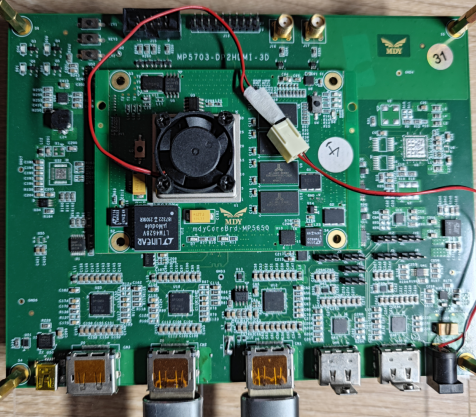

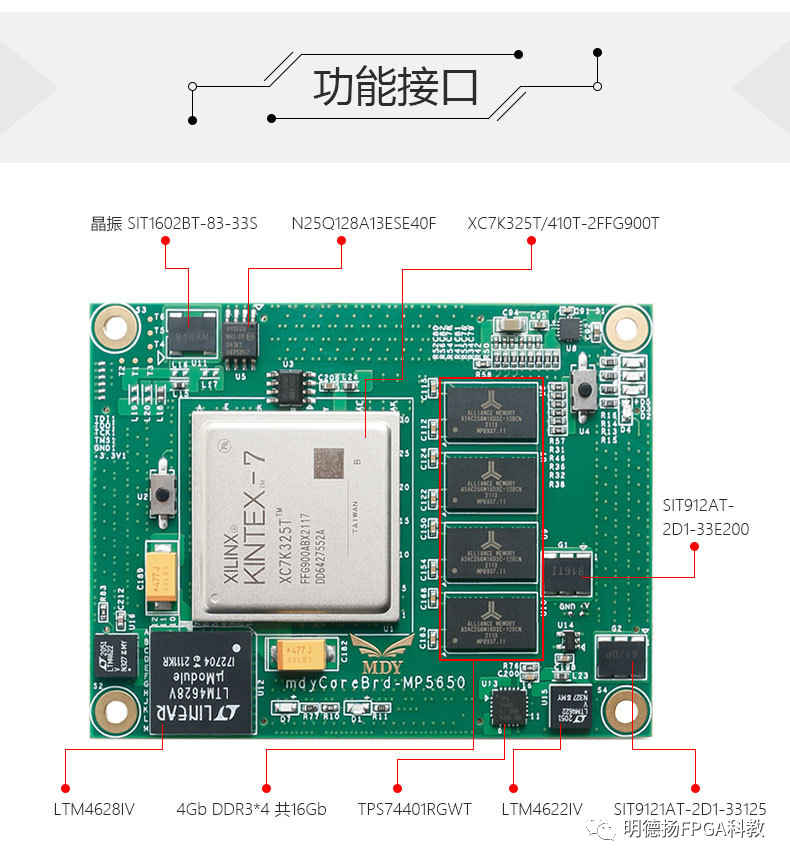

明德揚(MDY)為某公司研制的被動立體轉主動立體視頻模塊,該模塊將3840×1080/60Hz視頻轉成1920×1080/120Hz視頻。視頻輸入接口為DP,輸出接口為DP和HDMI,基于Xilinx K7325t的高速收發器,特點是無需外圍接收/發送芯片,大大簡化了硬件設計。該視頻接口轉換模塊如圖1所示,其中k7核心板型號為MP5650,底板和核心板均為明德揚自研產品。

本文簡單介紹了Xilinx官方的DP例程的建立步驟。

圖1被動立體轉主動立體視頻模塊

圖2 MP5650核心板

2、工具

Vivado 2019.1;

參考的Xilinx手冊編號:PG233、UG476、UG475。

3、操作步驟

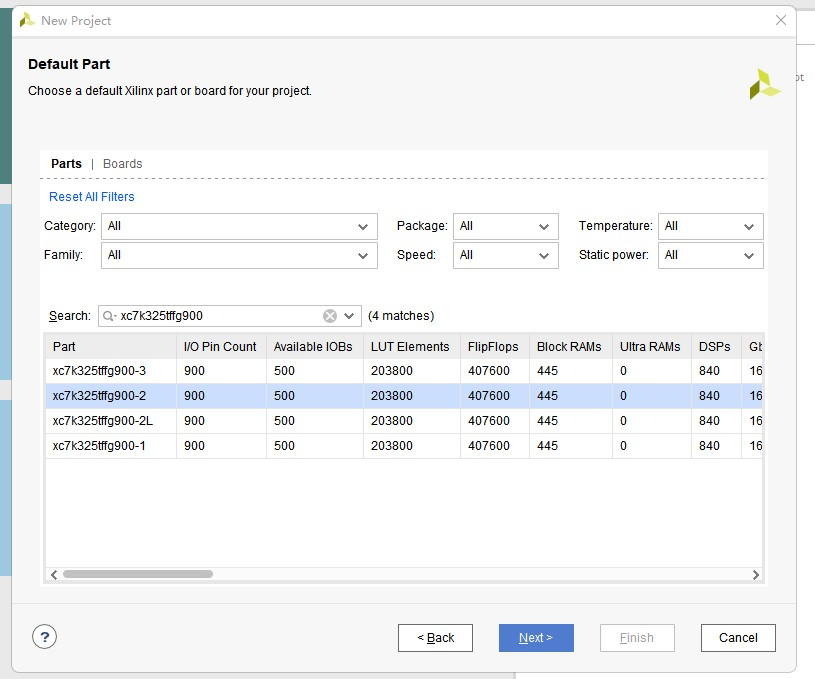

(1)新建一個vivado工程,平臺選擇xc7k325tffg900-2。

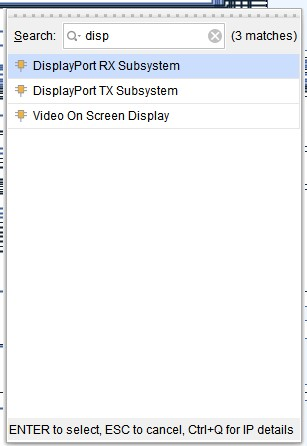

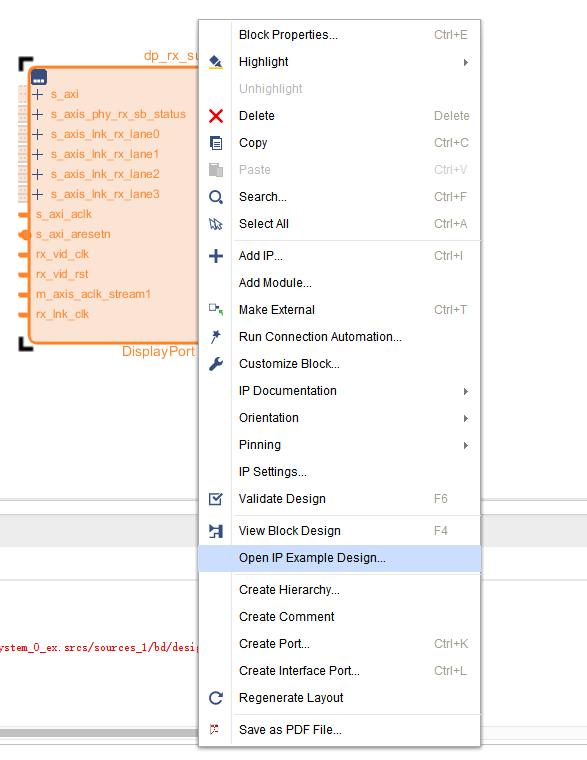

(2)創建Block Design,選擇Displayport RX Subsystem IP,并打開IP example design。

(3)待工程建立完畢后,生成bit文件并導出到SDK。

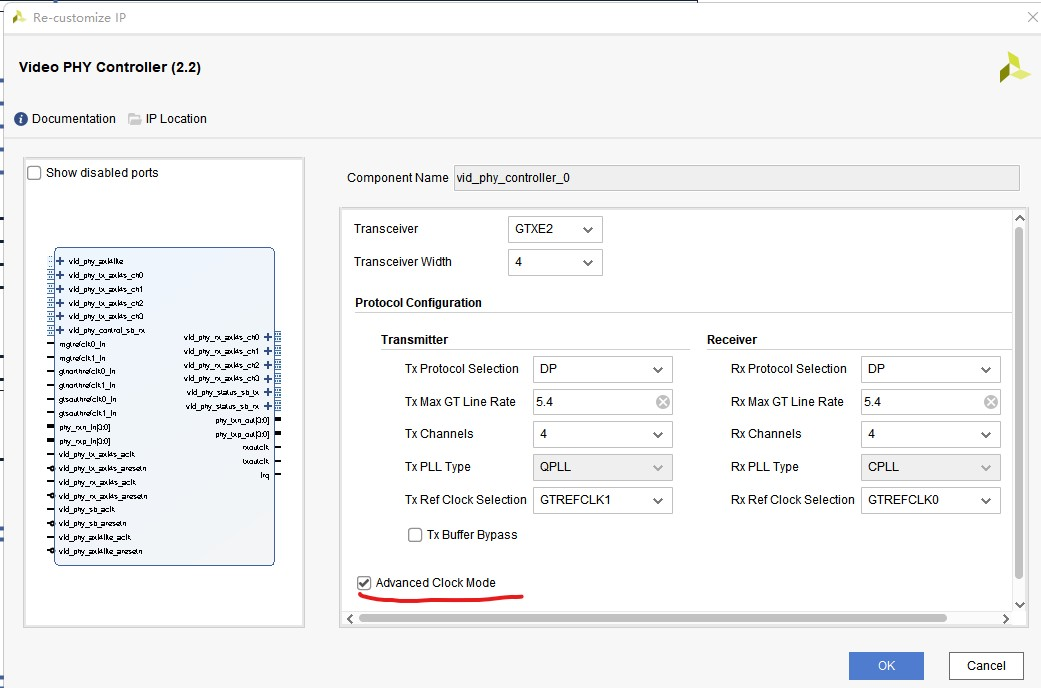

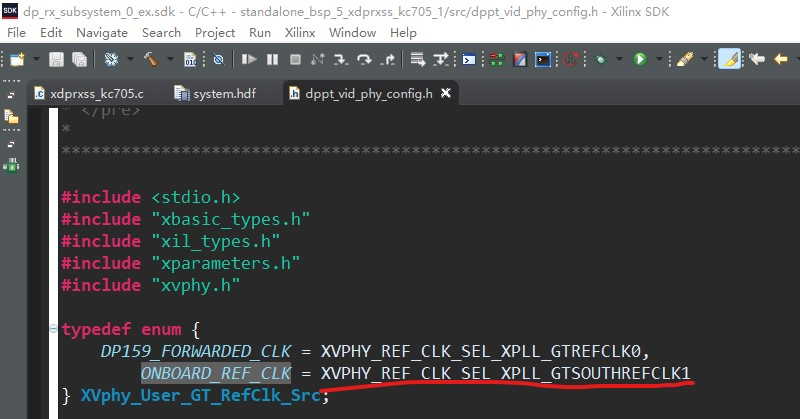

(4)值得注意的是,在硬件連線方面,如果FPGA高速收發器的參考時鐘沒有按照官方的連線方式,則需要更改時鐘的輸入選擇。更改方式如下:

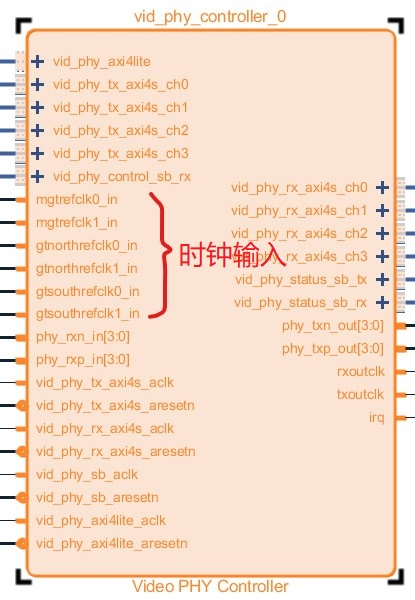

A. 勾選PHY Controller IP核的Advanced Clock Mode選項,IP核會多顯示出4路時鐘gtnorthrefclk0_in、gtnorthrefclk1_in、gtsouthrefclk0_in、gtsouthrefclk0_in。

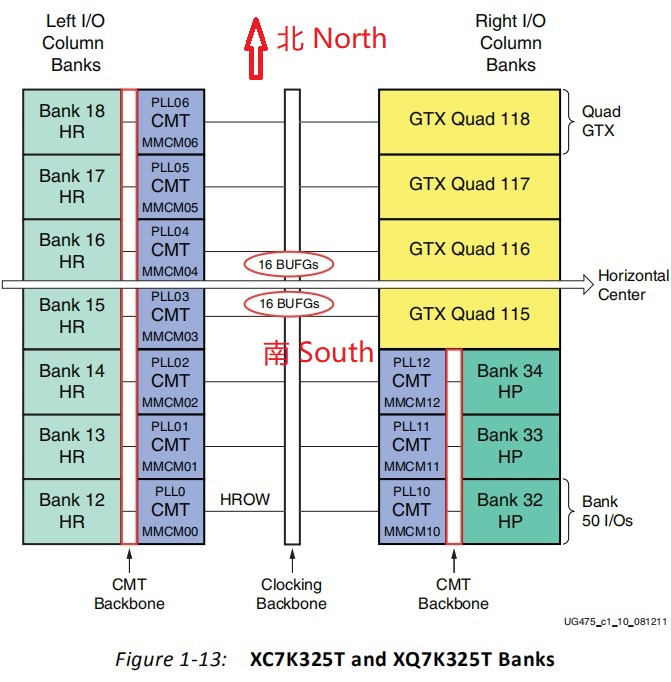

B. 官方手冊UG476中并未給出north和south參考時鐘的具體位置,但結合手冊UG476和UG475,可以得出Bank118在最北,Bank115在最南。假如我們當前工程使用Bank117,那么mgtrefclk在Bank117,gtnorthrefclk在Bank118,gtsouthrefclk在Bank116。

C. 硬件邏輯改完后,SDK中的驅動程序也需要改動。

溫馨提示:明德揚擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 前端模擬采集、射頻、電荷靈敏前置放大器

有相關需求可以聯系:蘭老師18011939283(微信同號)