一、背景

明德揚(MDY)在2022年承擔了多個高速ADC研發項目,今天給大家分享AD9747混合模式的作用。在ADDA系統中,AD前端采集到的帶通信號,經FPGA做數字信號處理后通過DAC進行數模轉換輸出。AD輸出采用欠采樣模式,FPGA數字信號處理的時鐘與AD時鐘相等,而DA的時鐘需要2倍以上的AD時鐘。

二、AD9747正常模式和混合模式對比

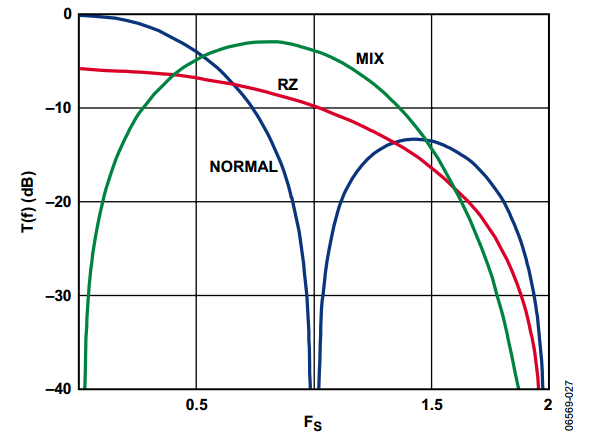

由于被采樣的信號是一個頻帶信號,即使采樣速率不滿足奈奎斯特采樣定律(即2倍最大頻率)也是可以在數字域通過算法將信號重建。由于一般DA的工作模式是直通模式(也就是AD9747的NORMAL模式),根據奈奎斯特采樣定律可以畫出該模式下的傳輸函數,如圖1中的藍色曲線(NORMAL):

圖1 不同模式下DA的傳輸函數曲線

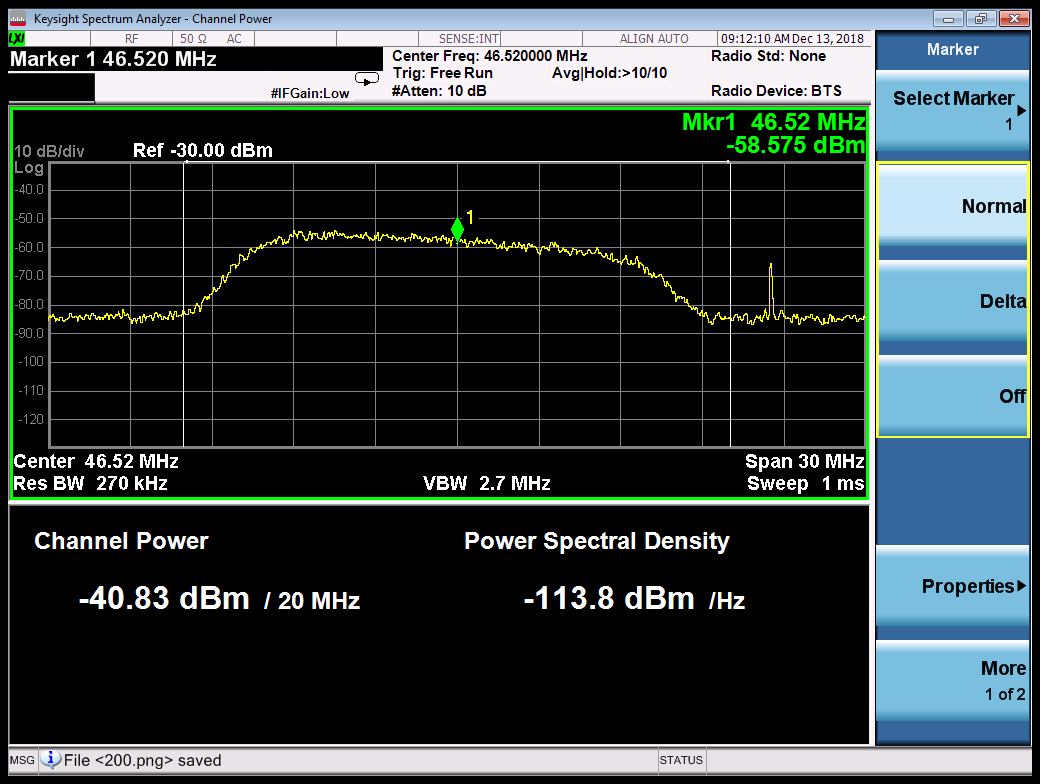

假設現在使Fs=62MHz,去輸出我們的頻帶信號,那么很顯然,輸出頻帶信號的頻譜越接近Fs的部分就越會被削弱的厲害,實際也做了測試,如圖2所示:

圖2 NORMAL模式下,信號46.52MHz±10.23MHz

從圖像可以看出,DA輸出的包絡的右半部分被削的很厲害,因此可以得出結論:即使能在數字域將信號完美重建,只要DA工作在直通模式,且不滿足奈奎斯特采樣定律的情況下,那么DA輸出的包絡肯定會失真。所以想要在此模式下保證包絡不失真,就必須要將DA的時鐘增大,使其滿足奈奎斯特采樣定律。

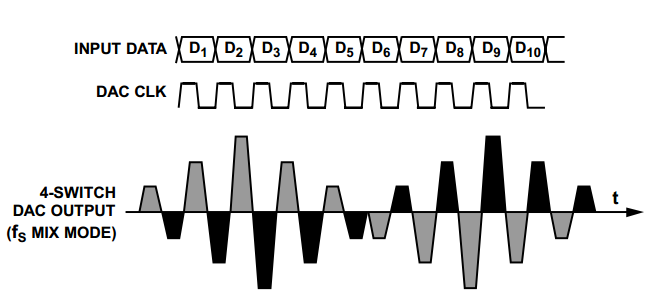

在混合模式中,其工作方式為:信號經過DAC采樣后產生兩路信號,其中一路是DAC輸出信號的反向輸出,另一路是DAC輸出信號的延時輸出,這兩個信號通過一個高速電子開關合成,形成如圖3所示的波形:

圖3 混合模式下DAC的輸出波形

可以看出,在DAC采樣時鐘的前半個周期內輸出了采樣數據正的幅值,后半周期輸出采樣信號負的賦值,這樣能更好的加強信號的高頻成分。其傳輸曲線如圖1中的綠色曲線(MIX)所示。

假設DAC的采樣時鐘是62MHz,要輸出的頻帶信號的中心頻點為46.52MHz,正好在該傳輸曲線的最高點,也就是0.75Fs處。在整個帶內的增益(帶寬20MHz,0.58Fs~0.91Fs)也是相對平坦的。最高點處的增益小了約2.5dB,因此最終在測量直通時的增益理論上也會減少。后期可以通過增加數字域的增益來彌補這個問題。

綜上所述,AD9747的混合模式可以使AD、FPGA、DA使用同一個頻率的時鐘,這樣可以帶來以下幾點好處:

① DA時鐘頻率降低,功耗也會降低;

② 時鐘系統可以直接使用時鐘分配器,將一路輸入時鐘分配至各個模塊,而不需要使用鎖相環芯片。

溫馨提示:明德揚擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 前端模擬采集、射頻、電荷靈敏前置放大器

有相關需求可以聯系:蘭老師18011939283(微信同號)